#### Wy ugr

### **Sumario**

- > Introducción

- ✓ Síntesis NAND/NOR

- ✓ Riesgos en circuitos combinacionales

- > Multiplexores y demultiplexores

- ✓ Diseño con multiplexores

- ✓ Acceso a buses y selección de datos

- > Codificación

- ✓ Representación en complementos

- ✓ Aritmética decimal BCD

- √ Codificadores y decodificadores

- ✓ Circuitos aritméticos

#### Introducción

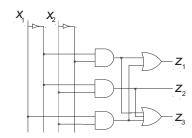

Circuito de conmutación (digital): cualquier sistema mecánico, eléctrico, etc., con entradas y salidas digitales (binarias).

| <i>X</i> <sub>1</sub> | <i>X</i> <sub>2</sub> | <i>z</i> <sub>1</sub> | <b>Z</b> <sub>2</sub> | <b>Z</b> <sub>3</sub> |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0                     | 0                     | 1                     | 0                     | 1                     |

| 0                     | 1                     | 1<br>0<br>0           | 1                     | 1                     |

| 1                     | 0                     | 0                     | 0                     | 0                     |

| 1                     | 1                     | 1                     | 0                     | 1                     |

Electrónica Digital - Circuitos lógicos combinacionales

### Introducción

- > Los circuitos combinacionales básicamente corresponde a la implementación de una o varias funciones de conmutación.

- Los procedimientos de síntesis vistos en el tema anterior proporcionan implementaciones en dos niveles: AND-OR (suma de productos) y OR-AND (producto de sumas).

- > Es posible trasladar las realizaciones en dos niveles a implementaciones con puertas **NAND** o puertas **NOR**.

#### Síntesis NAND/NOR

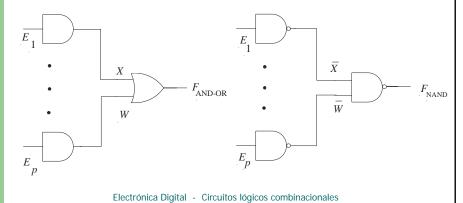

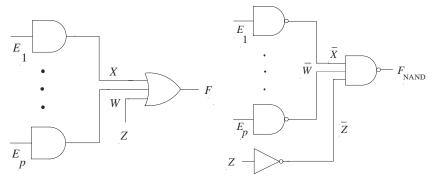

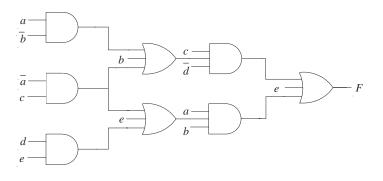

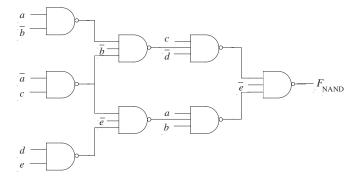

➤ Teorema: dado un circuito de dos niveles AND-OR (OR-AND), si todas las puertas del circuito se sustituyen por puertas NAND (NOR), la función realizada es la misma.

#### **Síntesis NAND/NOR**

Teorema: dado un circuito de dos niveles AND-OR (OR-AND), si todas las puertas del circuito se sustituyen por puertas NAND (NOR), la función realizada es la misma.

#### Síntesis NAND/NOR

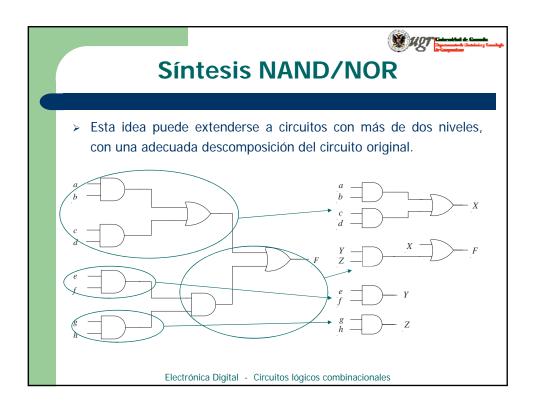

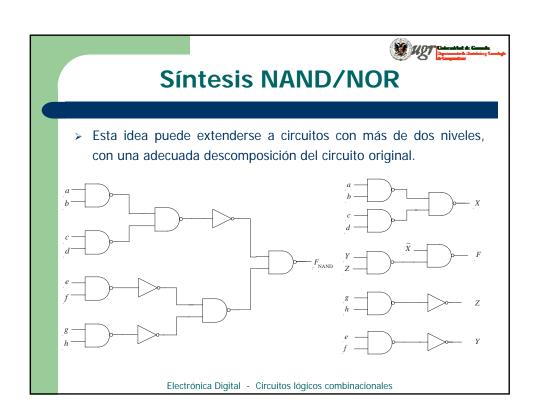

> Esta idea puede extenderse a circuitos con más de dos niveles, con una adecuada descomposición del circuito original.

Electrónica Digital - Circuitos lógicos combinacionales

### **Síntesis NAND/NOR**

> Esta idea puede extenderse a circuitos con más de dos niveles, con una adecuada descomposición del circuito original.

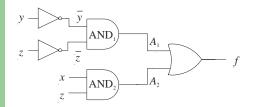

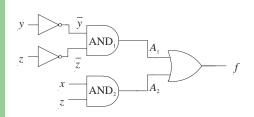

### Riesgos en circuitos combinacionales

- > En un circuito combinacional existe un **riesgo estático** si en una transición de las entradas en la que la salida debe de permanecer constante, ésta cambia su valor momentáneamente.

- > **Ejemplo:**  $f(x,y,z)=xz+\overline{y}\overline{z}$

| $x^{yz}$ | 00  | 01  | 11 | 10 |

|----------|-----|-----|----|----|

| 0        | 1   |     |    |    |

| 1        | 1 + | - 1 | 1  |    |

Electrónica Digital - Circuitos lógicos combinacionales

### wugr .....

## Riesgos en circuitos combinacionales

- > En un circuito combinacional existe un **riesgo estático** si en una transición de las entradas en la que la salida debe de permanecer constante, ésta cambia su valor momentáneamente.

- > **Ejemplo:**  $f(x,y,z)=xz+\overline{yz}$

#### Riesgos en circuitos combinacionales

- > En un circuito combinacional existe un **riesgo dinámico** si en una transición de las entradas en la que la salida ha de cambiar de 0 a 1, o viceversa, la salida sufre transiciones extras antes de alcanzar su valor final.

- Los riesgos estáticos o dinámicos asociados a transiciones de las entradas en las que sólo cambia una entrada se denominan riesgos lógicos.

- Los riesgos lógicos están provocados por los retardos asociados a la propagación de las señales en los circuitos de conmutación.

- Los riesgos dinámicos son consecuencia de los estáticos (evitables si la realización incluye todos los implicantes primos).

Electrónica Digital - Circuitos lógicos combinacionales

### Riesgos en circuitos combinacionales

- Los riesgos asociados a transiciones de las entradas en las que cambia más de una entrada se denominan riesgos funcionales.

- > Los riesgos funcionales no dependen de la forma del realización ni de la función concreta, al tiempo que son inevitables (salvo que se limiten las transiciones en la entrada a cambios individuales).

| xy | .00  | 01         | 11  | 10 |

|----|------|------------|-----|----|

| 00 | 1-   | <b>→</b>   |     |    |

| 01 | \ \_ | <b>→</b> 1 | 1   | -1 |

| 11 |      |            | 1 - | _+ |

| 10 | 1    | 1          |     |    |

#### **Sumario**

- > Introducción Introducción

- ✓ Síntesis NAND/NOR

- ✓ Riesgos en circuitos combinacionales

- > Multiplexores y demultiplexores

- ✓ Diseño con multiplexores

- ✓ Acceso a buses y selección de datos

- Codificación

- ✓ Representación en complementos

- ✓ Aritmética decimal BCD

- ✓ Codificadores y decodificadores

- ✓ Circuitos aritméticos

Electrónica Digital - Circuitos lógicos combinacionales

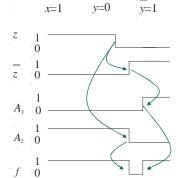

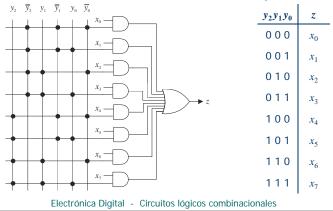

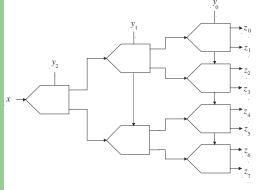

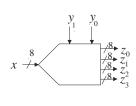

## Multiplexores y demultiplexores

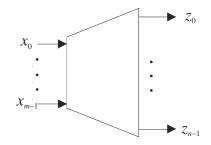

➤ Un multiplexor es un circuito combinacional para el enrutamiento de la información. Consta de n entradas de control y 2<sup>n</sup> entradas de datos, con una única salida (multiplexor 2<sup>n</sup> a 1).

| $y_2y_1y_0$ | z                     |

|-------------|-----------------------|

| 0 0 0       | $x_0$                 |

| 0 0 1       | $x_1$                 |

| 0 1 0       | $x_2$                 |

| 0 1 1       | $x_3$                 |

| 100         | $x_4$                 |

| 101         | <i>x</i> <sub>5</sub> |

| 110         | $x_6$                 |

| 111         | <i>x</i> <sub>7</sub> |

Un multiplexor es un circuito combinacional para el enrutamiento de la información. Consta de n entradas de control y 2<sup>n</sup> entradas de datos, con una única salida (multiplexor 2<sup>n</sup> a 1).

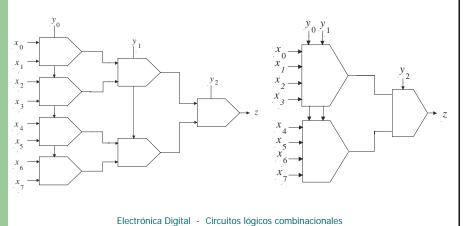

# Multiplexores y demultiplexores

> Pueden combinarse multiplexores 2 a 1, 4 a 1, etc., para conseguir diferentes estructuras.

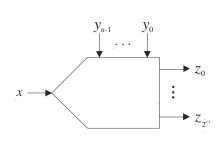

$\triangleright$  Un **demultiplexor** es un circuito combinacional para el enrutamiento de la información. Consta de n entradas de control, una entrada de datos y  $2^n$  salidas (demultiplexor 1 a  $2^n$ ).

| $y_2 y_1 y_0$                                 | z <sub>7</sub> | $z_6$ | $z_5$ | $z_4$ | $z_3$ | $z_2$ | $z_1$ | $z_0$ |

|-----------------------------------------------|----------------|-------|-------|-------|-------|-------|-------|-------|

| 0 0 0                                         | 0              | 0     | 0     | 0     | 0     | 0     | 0     | х     |

| 0 0 1                                         | 0              | 0     | 0     | 0     | 0     | 0     | x     | 0     |

| 010                                           | 0              | 0     | 0     | 0     | 0     | x     | 0     | 0     |

| 0 1 1                                         | 0              | 0     | 0     | 0     | х     | 0     | 0     | 0     |

| 100                                           | 0              | 0     | 0     | x     | 0     | 0     | 0     | 0     |

| 1 0 1                                         | 0              | 0     | x     | 0     | 0     | 0     | 0     | 0     |

| 110                                           | 0              | x     | 0     | 0     | 0     | 0     | 0     | 0     |

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | х              | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

> Un **demultiplexor** es un circuito combinacional para el enrutamiento de la información. Consta de n entradas de control, una entrada de datos y  $2^n$  salidas (demultiplexor 1 a  $2^n$ ).

| $y_2 y_1 y_0$                                          | z <sub>7</sub> | $z_6$ | $z_5$ | $z_4$ | $z_3$ | $z_2$ | $z_1$ | $z_0$ |

|--------------------------------------------------------|----------------|-------|-------|-------|-------|-------|-------|-------|

| 0 0 0                                                  | 0              | 0     | 0     | 0     | 0     | 0     | 0     | х     |

| 0 0 1                                                  | 0              | 0     | 0     | 0     | 0     | 0     | х     | 0     |

| 0 1 0                                                  | 0              | 0     | 0     | 0     | 0     | x     | 0     | 0     |

| 0 1 1                                                  | 0              | 0     | 0     | 0     | x     | 0     | 0     | 0     |

| 100                                                    | 0              | 0     | 0     | х     | 0     | 0     | 0     | 0     |

| 1 0 1                                                  | 0              | 0     | х     | 0     | 0     | 0     | 0     | 0     |

| 110                                                    | 0              | x     | 0     | 0     | 0     | 0     | 0     | 0     |

| y2y1y0   0 0 0   0 0 1   0 1 0   0 1 1   1 0 0   1 1 1 | х              | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Electrónica Digital - Circuitos lógicos combinacionales

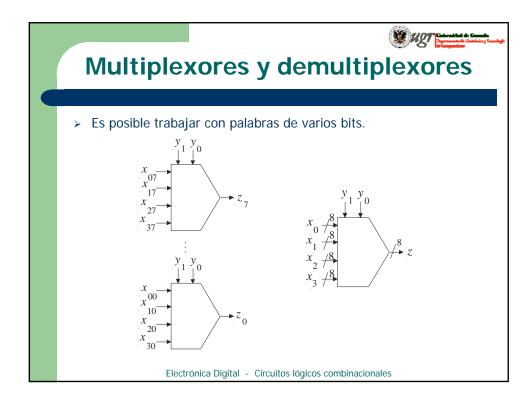

## **Multiplexores y demultiplexores**

> Pueden combinarse demultiplexores 1 a 2, 1 a 4, etc., para conseguir diferentes estructuras, o trabajar con palabras de varios bits.

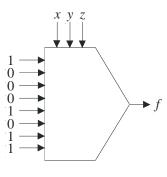

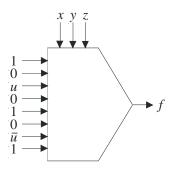

- Los multiplexores pueden emplearse como módulos lógicos universales:

- $\checkmark$  un multiplexor con n entradas de control permite sintetizar cualquier función de conmutación de n variables.

| xyz   | f(x,y,z) |

|-------|----------|

| 000   | 1        |

| 0 0 1 | 0        |

| 010   | 0        |

| 011   | 0        |

| 100   | 1        |

| 101   | 0        |

| 110   | 1        |

| 111   | 1        |

Electrónica Digital - Circuitos lógicos combinacionales

### **Q**ugr

## Multiplexores y demultiplexores

- Los multiplexores pueden emplearse como módulos lógicos universales:

- $\checkmark$  un multiplexor con n entradas de control puede sintetizar funciones de conmutación de n+1 variables.

| x y z | f(x,y,z)       |

|-------|----------------|

| 000   | 1              |

| 0 0 1 | 0              |

| 010   | и              |

| 0 1 1 | 0              |

| 100   | 1              |

| 101   | 0              |

| 110   | $\overline{u}$ |

| 111   | 1              |

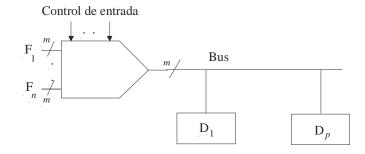

#### Acceso a buses

- ➢ Bus: subsistema para transmisión de información en un sistema digital formado por m hilos, siendo m el número de bits a transmitir simultáneamente.

- ➤ En sistemas digitales complejos, gran cantidad de subsistemas han de compartir información, con lo que se incluyen diferentes buses a los que tiene acceso diferentes subsistemas.

- La conexión directa de las diferentes fuentes y destinos de información a los buses, así como la interconexión entre diferentes buses puede causar conflictos (tema 5), que pueden evitarse con el uso de multiplexores y demultiplexores.

Electrónica Digital - Circuitos lógicos combinacionales

#### Acceso a buses

➢ Bus: subsistema para transmisión de información en un sistema digital formado por m hilos, siendo m el número de bits a transmitir simultáneamente.

#### **Sumario**

- > Introducción

- ✓ Síntesis NAND/NOR

- ✓ Riesgos en circuitos combinacionales

- > Multiplexores y demultiplexores

- ✓ Diseño con multiplexores

- ✓ Acceso a buses y selección de datos

- Codificación

- ✓ Representación en complementos

- ✓ Aritmética decimal BCD

- ✓ Codificadores y decodificadores

- ✓ Circuitos aritméticos

Electrónica Digital - Circuitos lógicos combinacionales

#### Codificación

- > **Sistema digital:** sistema en el que se genera, almacena, procesa y/o transmite información representada por señales digitales.

- Señal digital: señal limitada a tomar valores discretos determinados.

- > Bit: cantidad mínima de información (0/1).

#### Codificación

- Cuando los sistemas digitales procesan información que no es estrictamente binaria, es necesario representar dicha información utilizando señales binarias: codificación.

- > Existen diferentes códigos para representar la información en función de su contenido y la aplicación:

- ✓ codificación ASCII (*American Standard Code for Information Interchange*): caracteres alfanuméricos para su uso en ordenadores.

- Representación en complementos: la más extendida en circuitos aritméticos.

- ✓ BCD (*Binary-Coded Decimal*): codificación binaria de cifras decimales.

- ✓ Códigos para detección y corrección de errores.

Electrónica Digital - Circuitos lógicos combinacionales

#### Representación en complementos

- > El cálculo es una de las aplicaciones fundamentales de los sistemas digitales.

- > La implementación de sistemas digitales de cálculo requiere la representación con señales binarias de las cantidades numéricas.

- > En general, los sistemas digitales usan la base 2 en representaciones con peso, con lo que un número con *n* bits en la parte entera y *m* en la parte fraccionaria representa la cantidad:

$N.M = \underbrace{b_{n-1}2^{n-1} + ... + b_2 2^2 + b_1 2^1 + b_0 2^0 + b_{-1}2^{-1} + b_{-2}2^{-2} + ... + b_{-m}2^{-m}}_{\text{Parte entera}}$

>  $b_{n-1}$ : bit más significativo (MSB)

$b_{-m}$ : bit menos significativo (LSB)

#### Representación en complementos

> En esta representación en punto fijo la aritmética es muy sencilla, siendo la suma la operación básica:

Electrónica Digital - Circuitos lógicos combinacionales

### Complemento a uno

> En la representación en complemento a uno (a la base menos uno), dado un número positivo  $B=b_{n-1}...b_1b_0$ , el número -B se genera como:

$$-B = (2^n-1) - B$$

> En la práctica, el complemento a uno se genera muy fácilmente complementando cada uno de los bits del número:

$$-B=\overline{b_{n-1}}...\overline{b_1}\overline{b_0}$$

Para operar con cantidades en complemento a uno hay que añadir el posible acarreo de salida al bit menos significativo.

### Complemento a dos

► En la representación en complemento a dos (a la base), dado un número positivo  $B=b_{n-1}...b_1b_0$ , el número -B se genera como:

$$-B=2^n-B$$

En la práctica, el complemento a dos se genera complementando cada uno de los bits del número y sumando 1.

$$-B = \overline{b_{n-1}}...\overline{b_1}\overline{b_0} + 1$$

> El complemento a dos es el sistema usual de representación en punto fijo en sistemas digitales de cálculo.

Electrónica Digital - Circuitos lógicos combinacionales

## Complemento a dos

- > La gran ventaja de la representación en complemento a dos es:

- se puede operar como en binario natural sin ninguna consideración extra

- el bit más significativo corresponde al bit de signo (0 para números positivos y 1 para números negativos)

### Complemento a dos

- > La gran ventaja de la representación en complemento a dos es:

- ✓ se puede operar como en binario natural sin ninguna consideración extra

- ✓ el bit más significativo corresponde al bit de signo (0 para números positivos y 1 para números negativos)

- Aparecerá desbordamiento (overflow) cuando la suma de dos números positivos (negativos) produzca uno negativo (positivo):

Electrónica Digital - Circuitos lógicos combinacionales

#### Aritmética decimal BCD

- > La mayoría de sistemas digitales de cálculo emplean representación en complementos.

- En ocasiones es conveniente emplear aritmética decimal, representando cada cifra decimal por su valor binario: BCD (Binary-Coded Decimal).

- > Cada cifra decimal se codifica con 4 bits y agrupando estos caracteres de 4 bits se pueden representar cantidades decimales:

#### Aritmética decimal BCD

Es posible operar con cantidades representadas en BCD con una adecuada corrección (+6) en caso de generarse acarreo entre cifras:

Electrónica Digital - Circuitos lógicos combinacionales

#### Códigos para detección de errores

- > El único objeto de la codificación no es la representación de la información, sino que puede emplearse para detectar y/o corregir los posible errores que se produzcan en el sistema.

- > Durante la transmisión y almacenamiento de la información es posible que se altere el valor de algún bit (corrientes de fuga, radiación, etc.).

- > **Distancia** entre dos caracteres de un código: número de bits en que son distintos dichos caracteres. Los códigos vistos hasta ahora son de distancia 1.

### Códigos para detección de errores

- Los códigos de distancia 2 permiten detectar errores en un bit, ya que la alteración de una posición se traduce en un carácter que no pertenece al código.

- En los códigos de distancia 1 se puede añadir un bit extra de paridad (del número de 1s del carácter), con lo que se transforman en códigos de distancia 2 y pueden corregirse errores en un bit.

- ➤ En general, un código de distancia n permite detectar errores en n-1 bits de un carácter.

Electrónica Digital - Circuitos lógicos combinacionales

### Códigos para corrección de errores

- > Empleando un código de distancia 3 es posible detectar errores en dos bits, y corregir errores en uno de los bits.

- > Ejemplo:

A 00000 B 10101 C 11010 D 01111

- ✓ Un error en un bit de A puede traducirse en la recepción indistinta de 00000, 00001, 00010, 00100, 01000 ó 10000, que no pueden provenir de ningún otro carácter.

- ✓ Por tanto, el código del ejemplo permite corregir errores.

### Códigos para corrección de errores

- ➤ **Código Hamming:** código de  $2^n$ -1 bits (n≥2), de los que n son de paridad y  $2^n$ -1-n contienen información.

- √ cada bit de paridad (posición potencia de 2) establece paridad par entre él mismo y determinados bits de información

|   | $P_4P_2P_1$ |                         | $C_4C_2C_1$ | Error   |

|---|-------------|-------------------------|-------------|---------|

|   | 000         |                         | 0 0 0       | Ninguno |

| 1 | 001         |                         | 0 0 1       | 1       |

| 2 | 010         | $I_7I_6I_5P_4I_3P_2P_1$ | 010         | 2       |

| 3 | 011         |                         | 0 1 1       | 3       |

| 4 | 100         | (n=3)                   | 100         | 4       |

| 5 | 101         |                         | 101         | 5       |

| 6 | 110         |                         | 110         | 6       |

| 7 | 111         |                         | 111         | 7       |

Electrónica Digital - Circuitos lógicos combinacionales

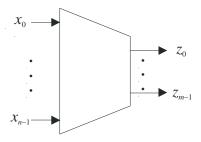

## **Codificadores y decodificadores**

$\triangleright$  Un **codificador** es un circuito combinacional con n (número de caracteres a codificar) entradas y m (número de bits del código) salidas (codificador de n a m).

## **Codificadores y decodificadores**

➤ Un codificador es un circuito combinacional con n (número de caracteres a codificar) entradas y m (número de bits del código) salidas (codificador de n a m).

| Entrada               | $z_4 z_3 z_2 z_1 z_0$ |

|-----------------------|-----------------------|

| Ninguna               | 00000                 |

| $x_0$                 | 00011                 |

| $x_1$                 | 00101                 |

| $x_2$                 | 00110                 |

| $x_3$                 | 01001                 |

| $x_4$                 | 01010                 |

| <i>x</i> <sub>5</sub> | 01100                 |

| $x_6$                 | 10001                 |

| <i>x</i> <sub>7</sub> | 10010                 |

| $x_8$                 | 10100                 |

| $x_9$                 | 11000                 |

| •                     | •                     |

Electrónica Digital - Circuitos lógicos combinacionales

0 0

0 0

## Codificadores y decodificadores

- En los codificadores sin prioridad se supone que sólo una entrada puede estar activa en cada momento.

- En los codificadores con prioridad varias entradas pueden estar activas en cada momento.

- > **Ejemplo:** codificador 4 a 2 con prioridad (3-2-1-0)

$$z_1 = x_2 + x_3$$

$z_0 = x_1 \overline{x_2} + x_3$

$x_3x_2x_1x_0$

0001

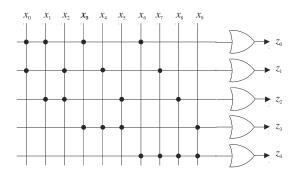

## **Codificadores y decodificadores**

- Muchos códigos para detección y corrección de errores incluyen la generación y comprobación de bits de **paridad**:

- ✓ la función EXOR permite generar y comprobar la paridad par.

- ✓ la función EXNOR permite generar y comprobar la paridad impar.

- > Otros circuitos muy habituales son los conversores de código, que permiten transformar los símbolos de un código a otro.

Electrónica Digital - Circuitos lógicos combinacionales

## **Codificadores y decodificadores**

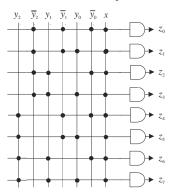

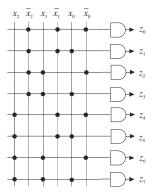

$\succ$  Un **decodificador** es un circuito combinacional con m (número de bits del código) entradas y n (número de caracteres a codificar) salidas (decodificador de m a n).

### **Codificadores y decodificadores**

> Un **decodificador** es un circuito combinacional con *m* (número de bits del código) entradas y *n* (número de caracteres a codificar) salidas (decodificador de *m* a *n*).

| $z_7 z_6 z_5 z_4 z_3 z_2 z_1 z_0$ |

|-----------------------------------|

| 00000001                          |

| 00000010                          |

| 00000100                          |

| 00001000                          |

| 00010000                          |

| 00100000                          |

| 01000000                          |

| 10000000                          |

|                                   |

Electrónica Digital - Circuitos lógicos combinacionales

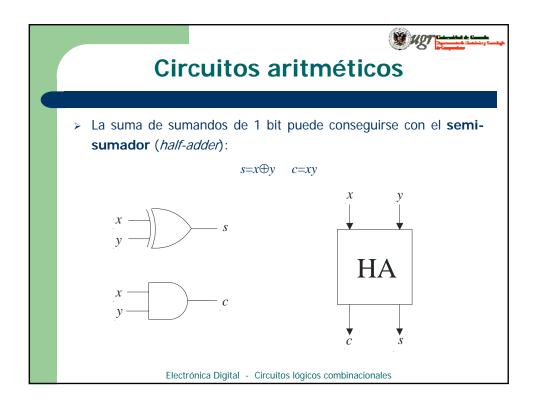

#### Circuitos aritméticos

- > El procesamiento de información en los sistemas digitales está basado normalmente en la realización de operaciones aritméticas:

- √ aplicaciones de cálculo

- ✓ aplicaciones basadas en algoritmos matemáticos (procesamiento digital de señales, procesamiento de imágenes, compresión, etc.)

- Una vez que la información de contenido aritmético está representada en la manera más adecuada (complementos, BCD, etc.) se puede procesar con los bloques combinacionales correspondientes.

- > La **suma** es la operación fundamental.

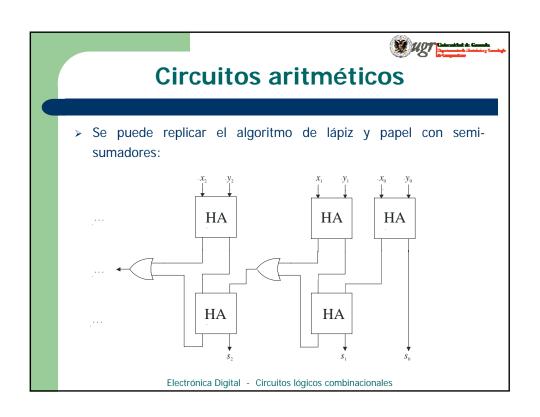

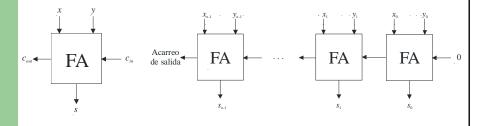

#### Circuitos aritméticos

> Si se incluyen en cada etapa los acarreos de entrada  $(c_{in})$  y salida  $(c_{out})$  se puede definir el sumador completo (full-adder):

$$s=x\oplus y\oplus c_{in}$$

$c_{out}=xy+xc_{in}+yc_{in}$

Electrónica Digital - Circuitos lógicos combinacionales

#### Circuitos aritméticos

> La resta está basada en los mismos principios que la suma, sustituyendo el acarreo por el adeudo:

$$r=x\oplus y$$

$d=\overline{x}y$

- Otras funciones aritméticas incluyen la suma BCD, comparadores, etc.

- Un bloque muy común en sistemas digitales es la ALU (*Arithmetic-Logic Unit*), que en función de unas entradas de control realiza diferentes operaciones aritméticas para las entradas de datos.