## **Sumario**

- > Introducción: elementos de memoria y registros

- Contadores

- ✓ Contadores síncronos y asíncronos

- ✓ Contadores con registros de desplazamiento

- > Sistemas secuenciales síncronos

- ✓ Máquinas de estados finitos: máquinas Mealy y Moore

- ✓ Implementación y minimización

- > Sistemas secuenciales asíncronos

- ✓ Definición y síntesis

- ✓ Ciclos, carreras y riesgos

#### Introducción

- En los sistemas mostrados hasta ahora, salvo los retardos asociados a la propagación de las señales, las salidas únicamente dependen de las entradas.

- En los sistemas secuenciales la salida en un instante dado depende de las entradas en dicho instante y de la historia del sistema.

- ✓ La historia del sistema está determinada por el estado del mismo en el instante inicial y los valores de las entradas desde dicho instante.

- ✓ Esto requiere que el sistema recuerde su historia, por lo que los sistemas secuenciales son sistemas con memoria.

Electrónica Digital - Circuitos lógicos secuenciales

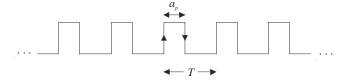

## Señales de reloj

- Las **señales de reloj** controlan el funcionamiento de los sistemas digitales y **cuantifican** la evolución del tiempo en los mismos.

- Una señal de reloj es, idealmente, una señal de pulsos periódica, caracterizada por el período y la anchura del pulso:

✓ Sistemas secuenciales síncronos: Sistemas sincronizados por flancos (subida o bajada) o nivel de la señal de reloj.

### Elementos de memoria

- > El elemento básico de memoria es el **biestable** (*latch*):

- ✓ Dos inversores en anillo permiten almacenar un valor lógico.

- > El biestable almacena un bit de información:

- $\checkmark$  Mientras que en el proceso de lectura no se extraiga demasiada energía del mismo, el valor de Q permanece inalterado.

- El proceso de escritura requiere conectar una de las variables a una fuente de energía suficiente con el valor que se desee escribir en el biestable.

Electrónica Digital - Circuitos lógicos secuenciales

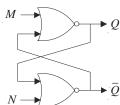

## Elementos de memoria

> El biestable básico puede mejorarse con entradas que permitan la escritura empleando puertas NAND o NOR.

| $\boldsymbol{A}$ | В | $Q_{n+1}$ | $\overline{Q}_{n+1}$ |

|------------------|---|-----------|----------------------|

| 0                | 0 | 1         | 1                    |

| 0                | 1 | 1         | 0                    |

| 1                | 0 | 0         | 1                    |

| 1                | 1 | $Q_n$     | $\overline{Q}_n$     |

| M | N | $Q_{n+1}$ | $\overline{Q}_{n+1}$ |

|---|---|-----------|----------------------|

| 0 | 0 | $Q_n$     | $\overline{Q_n}$     |

| 0 | 1 | 1         | 0                    |

| 1 | 0 | 0         | 1                    |

| 1 | 1 | 0         | 0                    |

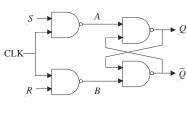

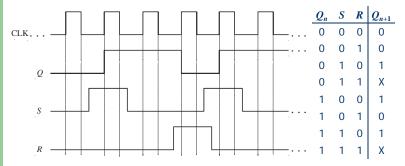

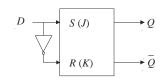

### **Biestable SR**

- Dos entradas para control de datos en sincronía con la entrada de reloj:

- ✓ si CLK=0 se aíslan las salidas de las entradas (almacenamiento).

- ✓ si CLK=1 las entradas pueden modificar la salida.

|                                                         | (SR = 0)  |

|---------------------------------------------------------|-----------|

| $Q_{n+1} = S + Q_n R$                                   | (SR = 0)  |

| $\mathcal{L}_{n+1} = \mathcal{L}_{n} + \mathcal{L}_{n}$ | (DII - 0) |

| 0 | _                |

|---|------------------|

| ~ | 0                |

| 1 | 0                |

| 0 | 1                |

| 1 | Χ                |

| 0 | 1                |

| 1 | 0                |

| 0 | 1                |

| 1 | Χ                |

|   | 1<br>0<br>1<br>0 |

Electrónica Digital - Circuitos lógicos secuenciales

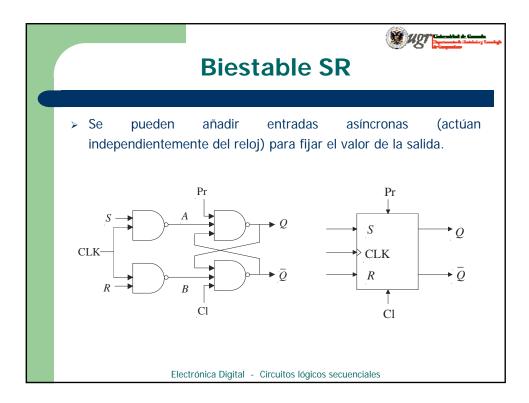

## **Biestable SR**

- Dos entradas para control de datos en sincronía con la entrada de reloj (por nivel):

- ✓ si CLK=0 se aíslan las salidas de las entradas (almacenamiento).

- ✓ si CLK=1 las entradas pueden modificar la salida.

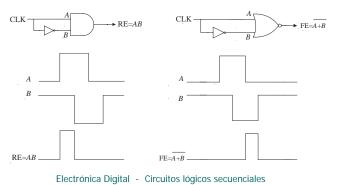

# Disparo por flancos

- > El disparo por nivel puede causar valores incorrectos si se producen transiciones incorrectas en las entradas.

- > Esto puede evitarse con el disparo por flanco, que puede incluirse en cualquier biestable:

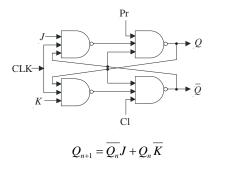

#### **Biestable JK**

- > En el biestable SR ha de evitarse una combinación de entradas para evitar indefiniciones.

- > Esto se resuelve con el biestable JK:

Electrónica Digital - Circuitos lógicos secuenciales

0

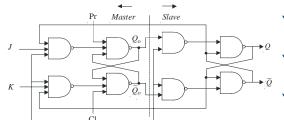

## Biestables master-slave

- > Los biestables JK pueden sufrir problemas de carreras:

- ✓ si JK=11 la salida oscila si el retardo de propagación de la señal a través del biestable es menor que la anchura del pulso de reloj.

- > Esto puede solventarse con un retardo suficiente entre entrada y salida o con una configuración *master-slave* :

- ✓ en CLK=1 el master capta la entrada

- √ en CLK=0 pasa al slave

- ✓ lectura y escritura simultáneas

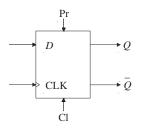

# Biestable D (Delay)

- Es uno de los más usados por su sencillez, con una sola entrada síncrona

- > El almacenamiento en un biestable D equivale a un retardo de un pulso de reloj para la información.

Electrónica Digital - Circuitos lógicos secuenciales

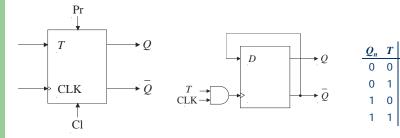

# Biestable T (Toggle)

> Tiene una única entrada síncrona que indica si la salida cambia o no en cada ciclo de reloj.

$$Q_{n+1} = \overline{Q_n}T + Q_n\overline{T}$$

### Tablas de excitación

Estas tablas indican las combinaciones de entradas necesarias en cada tipo de biestable para conseguir cualquier transición de la salida.

| $Q_n$ | $Q_{n+1}$ | S | R | $Q_n$ | $Q_{n+1}$ | J | K | _ | $Q_n$ | $Q_{n+1}$ | D | _ | $Q_n$ | $Q_{n+1}$ | T |

|-------|-----------|---|---|-------|-----------|---|---|---|-------|-----------|---|---|-------|-----------|---|

| 0     | 0         | 0 | _ | 0     | 0         | 0 | _ | = | 0     | 0         | 0 |   | 0     | 0         | 0 |

| 0     | 1         | 1 | 0 | 0     | 1         | 1 | _ |   | 0     | 1         | 1 |   | 0     | 1         | 1 |

| 1     | 0         | 0 | 1 | 1     | 0         | - | 1 |   | 1     | 0         | 0 |   | 1     | 0         | 1 |

| 1     | 1         | _ | 0 | 1     | 1         | _ | 0 |   | 1     | 1         | 1 |   | 1     | 1         | 0 |

Electrónica Digital - Circuitos lógicos secuenciales

## **Registros**

- Registro: sistema secuencial síncrono formado por agrupaciones de biestables con señales comunes de control y activados por la misma señal de reloj.

- Son elementos fundamentales en los sistemas digitales, en los que pueden desempeñar funciones diversas:

- ✓ almacenamiento de datos

- √ registros de desplazamiento

- √ adaptación serie-paralelo y paralelo-serie

- ✓ interfaz entre sistemas

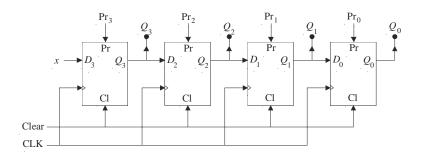

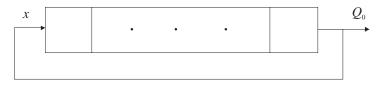

# Registros de desplazamiento

Un registro de desplazamiento está formado por biestables tipo D en los que salida de cada uno de ellos está conectada con la entrada del siguiente

Electrónica Digital - Circuitos lógicos secuenciales

## **Sumario**

- > Introducción: elementos de memoria y registros

- Contadores

- ✓ Contadores síncronos y asíncronos

- ✓ Contadores con registros de desplazamiento

- > Sistemas secuenciales síncronos

- ✓ Máquinas de estados finitos: máquinas Mealy y Moore

- ✓ Implementación y minimización

- > Sistemas secuenciales asíncronos

- ✓ Definición y síntesis

- ✓ Ciclos, carreras y riesgos

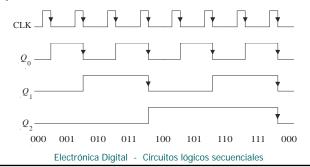

#### **Contadores**

- Contador: sistema secuencial con una entrada de reloj y m salidas:

- ✓ en cada pulso de reloj cambia el valor de las salidas, que recorren

cíclicamente una serie de configuraciones predeterminadas.

- ✓ puede incluir otras entradas de control (paso a un estado prefijado, carga en paralelo del estado, etc.).

- ✓ normalmente las configuraciones de las salidas responden a una cuenta de los pulsos de reloj.

- > Según la actuación de la señal de reloj se clasifican en:

- ✓ síncronos: la señal de reloj actúa sobre todos los biestables.

- ✓ asíncronos: la señal de reloj sólo actúa sobre uno de los biestables.

Electrónica Digital - Circuitos lógicos secuenciales

### **Contadores síncronos**

- > Un contador síncrono está formado por:

- ✓ una serie de biestables activados por una misma señal de reloj, con lo que cambian de estado simultáneamente.

- ✓ lógica combinacional que, a partir de las salidas de los biestables, sintetiza las entradas de excitación de los biestables.

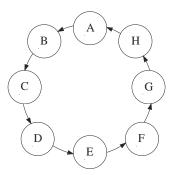

- > **Ejemplo:** diseñar un contador ascendente módulo 8 con biestables JK:

- ✓ se utilizará el procedimiento estándar para el diseño de sistemas secuenciales síncronos.

- ✓ en un sistema con n estados  $(2^{m-1} < n < 2^m)$  son necesarios al menos m biestables (3 en el ejemplo).

## **Contadores síncronos**

- ➤ La salida ha de recorrer los valores 000,001,010,...,110,111,000,...

- ✓ se construye la tabla de asignación de estados, siendo en este caso posible identificar salidas y estados.

| Asignación | $q^n$ | $q^{n+1}$ |

|------------|-------|-----------|

| 000        | Α     | В         |

| 0 0 1      | В     | С         |

| 010        | С     | D         |

| 011        | D     | Ε         |

| 100        | Ε     | F         |

| 101        | F     | G         |

| 110        | G     | Н         |

| 111        | Н     | Α         |

Electrónica Digital - Circuitos lógicos secuenciales

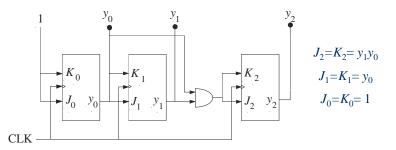

## **Contadores síncronos**

- > La salida ha de recorrer los valores 000,001,010,...,110,111,000,...

- √ tras realizar la asignación de estados, se construye la tabla de excitación de los biestables y se implementan dichas funciones.

| $q^n$     |   | $q^{n+1}$   |          | _        | _        |

|-----------|---|-------------|----------|----------|----------|

| $y_2y_1y$ | 0 | $y_2y_1y_0$ | $J_2K_2$ | $J_1K_1$ | $J_0K_0$ |

| 000       | C | 0 0 1       | 0 –      | 0 –      | 1 –      |

| 0.0       | 1 | 010         | 0 –      | 1 –      | - 1      |

| 010       | C | 011         | 0 –      | - 0      | 1 –      |

| 0.1       | 1 | 100         | 1 –      | - 1      | - 1      |

| 100       | О | 101         | - 0      | 0 –      | 1 –      |

| 10        | 1 | 110         | - 0      | 1 –      | - 1      |

| 110       | C | 111         | - 0      | - 0      | 1 –      |

| 11        | 1 | 000         | - 1      | - 1      | - 1      |

$$J_2 = K_2 = y_1 y_0$$

$$J_1 = K_1 = y_0$$

$$J_0 = K_0 = 1$$

### **Contadores síncronos**

- ➤ La salida ha de recorrer los valores 000,001,010,...,110,111,000,...

- ✓ tras realizar la asignación de estados, se construye la tabla de excitación de los biestables y se implementan dichas funciones.

Electrónica Digital - Circuitos lógicos secuenciales

## **Contadores síncronos**

- > **Ejemplo:** diseñar un contador síncrono con biestables D que reproduzca la secuencia 101,010,011,101,000,100,...:

- es un sistema con 6 estados, pero no es posible identificar la salida con la asignación de estados.

| ,          | 1     |           |

|------------|-------|-----------|

| Asignación | $q^n$ | $q^{n+1}$ |

| 0 0 0      | Α     | В         |

| 0 0 1      | В     | С         |

| 010        | С     | D         |

| 0 1 1      | D     | Ε         |

| 100        | Ε     | F         |

| 101        | F     | Α         |

### **Contadores síncronos**

- > **Ejemplo:** diseñar un contador síncrono con biestables D que reproduzca la secuencia 101,010,011,101,000,100,...:

- ✓ es un sistema con 6 estados, pero no es posible identificar la salida con la asignación de estados.

| $q^n$       | $q^{n+1}$   |       |       |       |               |                                                                               |

|-------------|-------------|-------|-------|-------|---------------|-------------------------------------------------------------------------------|

| $y_2y_1y_0$ | $y_2y_1y_0$ | $D_2$ | $D_1$ | $D_0$ | $z_2 z_1 z_0$ | $D_2 = y_2 \overline{y_1} \overline{y_0} + \overline{y_2} y_1 y_0$            |

| 000         | 001         | 0     | 0     | 1     | 101           |                                                                               |

| 0 0 1       | 010         | 0     | 1     | 0     | 010           | $D_1 = \overline{y_2} \overline{y_1} y_0 + \overline{y_2} y_1 \overline{y_0}$ |

| 010         | 011         | 0     | 1     | 1     | 0 1 1         | $D_0 = \overline{y}_1 \overline{y}_0 + \overline{y}_2 \overline{y}_0$         |

| 011         | 100         | 1     | 0     | 0     | 101           | $z = v v + v v + \overline{v} \overline{v} \overline{v}$                      |

| 100         | 101         | 1     | 0     | 1     | 000           | $z_2 = y_2 y_0 + y_1 y_0 + \overline{y_2} \overline{y_1} \overline{y_0}$      |

| 101         | 000         | 0     | 0     | 0     | 100           | $z_1 = y_1 \overline{y_0} + \overline{y_2} \overline{y_1} y_0$                |

| 110         | 000         | 0     | 0     | 0     |               | $z_0 = y_1 + \overline{y_2} \overline{y_1} \overline{y_0}$                    |

| 111         | 000         | 0     | 0     | 0     |               | 0 1 1 2 2 1 0                                                                 |

Electrónica Digital - Circuitos lógicos secuenciales

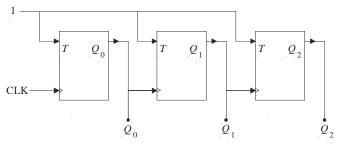

## **Contadores asíncronos**

- > En un contador asíncrono:

- ✓ la señal de reloj actúa sólo sobre uno de los biestables del sistema.

- ✓ sobre el resto de biestables actúan las salidas de otros biestables.

- ✓ la lógica combinacional adicional suele ser muy reducida.

- > Ejemplo: contador ascendente asíncrono módulo 8

#### Contadores asíncronos

- > En un contador asíncrono:

- ✓ la señal de reloj actúa sólo sobre uno de los biestables del sistema.

- ✓ sobre el resto de biestables actúan las salidas de otros biestables.

- ✓ la lógica combinacional adicional suele ser muy reducida.

- > Ejemplo: contador ascendente asíncrono módulo 8

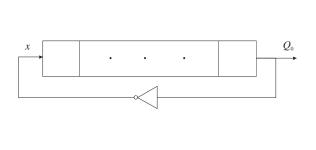

### Contadores con registros de desplazamiento

- Los registros de desplazamiento son el bloque constitutivo básico de varios tipos de sistemas secuenciales:

- ✓ contadores en anillo.

- ✓ contadores Johnson.

- ✓ generadores de secuencias.

- ➤ Un contador en anillo funciona como una memoria circulante de m bits que almacena una secuencia de m-1 ceros y un uno.

#### Contadores con registros de desplazamiento

Un contador Johnson (o Moëbius) consiste en un registro de desplazamiento de m bits que, dependiendo de la carga inicial, puede generar 2m configuraciones diferentes.

| $t_n$ | $Q_4Q_3Q_2Q_1Q_0$ |

|-------|-------------------|

| 1     | 00000             |

| 2     | 10000             |

| 3     | 11000             |

| 4     | 11100             |

| 5     | 11110             |

| 6     | 11111             |

| 7     | 01111             |

| 8     | 00111             |

| 9     | 00011             |

| 10    | 00001             |

| 11    | 00000             |

|       | •                 |

Electrónica Digital - Circuitos lógicos secuenciales

## Contadores con registros de desplazamiento

- > Un generador de secuencias consta de un registro de desplazamiento realimentado por la salida de una cierta lógica combinacional.

- > El procedimiento de síntesis está basado en definir la entrada x a partir de las salidas  $Q_{m-1}\cdots Q_0$ :

- determinar la longitud necesaria del registro de desplazamiento a partir de:

- o número de estados necesarios (caracteres distintos en el registro en cada instante)

- $\circ f(1,...,1) \neq 1 \text{ y } f(0,...,0) \neq 0$

- $\checkmark$  obtener la entrada de realimentación como  $x=f(Q_{m-1},...,Q_0)$

## Contadores con registros de desplazamiento

- > **Ejemplo:** diseñar un generador de secuencia para 00010001...

- ✓ Son necesarios al menos dos biestables (4 estados diferentes del registro), pero es evidente que dos biestables no son suficientes:

| $t_n$ | $Q_1Q_0$ |          |

|-------|----------|----------|

| 1     | 0 0      | <b>←</b> |

| 2     | 0 0      | <b>←</b> |

| 3     | 1 0      |          |

| 4     | 0 1      |          |

✓ La situación anterior no es válida ya que en dos instantes diferentes el contenido del registro es el mismo, con lo que son necesarios tres biestables.

Electrónica Digital - Circuitos lógicos secuenciales

### Contadores con registros de desplazamiento

- > **Ejemplo:** diseñar un generador de secuencia para 00010001...

- La situación anterior no es válida ya que en dos instantes diferentes el contenido del registro es el mismo, con lo que son necesarios tres biestables

|       |             |   |             |   | (111)                             |

|-------|-------------|---|-------------|---|-----------------------------------|

|       |             |   | $Q_2Q_1Q_0$ | f |                                   |

|       |             |   | 0 0 0       | 1 |                                   |

| $t_n$ | $Q_2Q_1Q_0$ | f | 0 0 1       | 0 | $(100) \qquad (001) \qquad (011)$ |

| 1     | 000         | 1 | 0 1 0       | 0 | $\gamma$                          |

| 2     | 100         | 0 | 0 1 1       | _ |                                   |

| 3     | 010         | 0 | 100         | 0 | (110)                             |

| 4     | 0 0 1       | 0 | 101         | _ | <u> </u>                          |

|       |             |   | 110         | _ | 101                               |

|       |             |   | 111         | 0 |                                   |

|       |             |   | ·           |   | $J=Q_2Q_1Q_0$                     |

#### **Sumario**

- Introducción: elementos de memoria y registros

- Contadores

- ✓ Contadores síncronos y asíncronos

- ✓ Contadores con registros de desplazamiento

- > Sistemas secuenciales síncronos

- ✓ Máquinas de estados finitos: máquinas Mealy y Moore

- ✓ Implementación y minimización

- > Sistemas secuenciales asíncronos

- ✓ Definición y síntesis

- ✓ Ciclos, carreras y riesgos

Electrónica Digital - Circuitos lógicos secuenciales

## Sistemas secuenciales síncronos

- > Un **sistema secuencial síncrono** es un sistema secuencial en el que una única señal de reloj controla la evolución del sistema.

- > Los contadores son un caso particular de los sistemas secuenciales síncronos, en los que no existen entradas externas que influyan en la evolución del sistema.

- > En general, en un sistema secuencial síncrono existen entradas externas que determinan, a partir del estado actual del sistema, la evolución del mismo.

- > Además, el sistema consta de ciertas salidas que pueden depender sólo del estado o del estado y las entradas externas.

### Sistemas secuenciales síncronos

- ➤ **Ejemplo:** diseñar un sistema digital que detecte símbolos incorrectos del código 441-2 en una transmisión serie.

- ✓ 0001, 0011, 0110, 1000, 1001 y 1011 son los caracteres inválidos.

- la salida del circuito se hará 1 cuando el carácter recibido sea uno de los anteriores

Electrónica Digital - Circuitos lógicos secuenciales

## Sistemas secuenciales síncronos

> **Ejemplo:** diseñar un sistema digital que detecte símbolos incorrectos del código 441-2 en una transmisión serie.

|   | $q^n$          | $q^{n+1}(y)$ | $y_2 y_1 y_0$ | 2      | 2     | 7     | 3     | 7    | 2     | 7   | 1   | 7   | 0   |  |

|---|----------------|--------------|---------------|--------|-------|-------|-------|------|-------|-----|-----|-----|-----|--|

|   | $y_3y_2y_1y_0$ | x=0          | x=1           | x=0    | x=1   | x=0   | x=1   | x=0  | x=1   | x=0 | x=1 | x=0 | x=1 |  |

| Α | 0000           | 0001         | 0010          | 0      | 0     | 0     | 0     | 0    | 0     | 0   | 1   | 1   | 0   |  |

| В | 0001           | 0011         | 0100          | 0      | 0     | 0     | 0     | 0    | 1     | 1   | 0   | 0   | 1   |  |

| С | 0010           | 0101         | 0110          | 0      | 0     | 0     | 0     | 1    | 1     | 1   | 0   | 1   | 0   |  |

| D | 0011           | 0111         | 1000          | 0      | 0     | 0     | 1     | 1    | 0     | 0   | 1   | 0   | 1   |  |

| Ε | 0100           | 1001         | 1010          | 0      | 0     | 1     | 1     | 1    | 1     | 0   | 1   | 1   | 0   |  |

| F | 0101           | 1011         | 1100          | 0      | 0     | 1     | 1     | 1    | 0     | 1   | 0   | 0   | 1   |  |

| G | 0110           | 1101         | 1110          | 0      | 0     | 1     | 1     | 0    | 0     | 1   | 0   | 1   | 0   |  |

| Н | 0111           | 0000         | 0000          | 0      | 1     | 0     | 0     | 1    | 1     | 1   | 1   | 1   | 1   |  |

| 1 | 1000           | 0000         | 0000          | 0      | 0     | 1     | 1     | 0    | 0     | 0   | 0   | 0   | 0   |  |

| J | 1001           | 0000         | 0000          | 0      | 0     | 1     | 1     | 0    | 0     | 0   | 0   | 1   | 1   |  |

| Κ | 1010           | 0000         | 0000          | 1      | 0     | 1     | 1     | 0    | 0     | 1   | 1   | 0   | 0   |  |

| L | 1011           | 0000         | 0000          | 1      | 1     | 1     | 1     | 0    | 0     | 1   | 1   | 1   | 1   |  |

| M | 1100           | 0000         | 0000          | 0      | 0     | 1     | 1     | 1    | 1     | 0   | 0   | 0   | 0   |  |

| N | 1101           | 0000         | 0000          | 1      | 1     | 1     | 1     | 1    | 1     | 0   | 0   | 1   | 1   |  |

| Р | 1110           | 0000         | 0000          | 0      | 0     | 1     | 1     | 1    | 1     | 1   | 1   | 0   | 0   |  |

| _ | 1111           |              |               | -      | -     | -     | -     | -    | -     | -   | -   | -   | -   |  |

| , | E              | lectrónica   | Digital - (   | Circui | tos l | ógico | s sec | uenc | iales | •   | •   | •   |     |  |

18

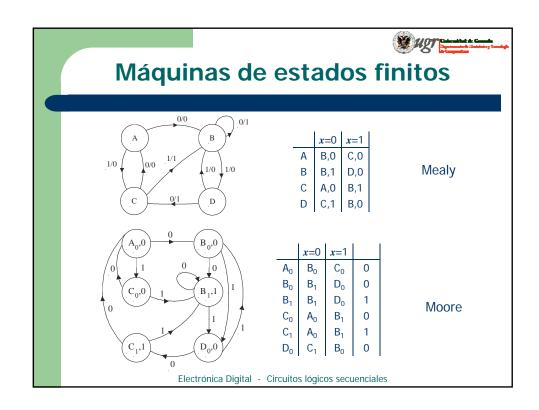

## Máquinas de estados finitos

- Los sistemas secuenciales síncronos también reciben el nombre de máquinas de estados finitos, ya que el número de variables de estado es finito.

- > Existen dos paradigmas diferentes para estos sistemas:

- máquinas Mealy: las salidas dependen de las entradas y el estado del sistema (están asociadas a las transiciones entre estados).

- ✓ máquinas Moore: las salidas dependen únicamente del estado.

- Ambos modelos son equivalentes, aunque generalmente la máquina Moore contará con más estados pero su síntesis será más sencilla.

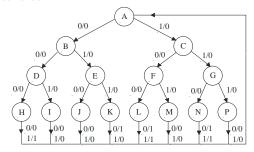

## Implementación y minimización

- > El procedimiento de síntesis de sistemas secuenciales síncronos se basa en la búsqueda de estados equivalentes y la consiguiente minimización de las variables de estado necesarias.

- Dos estados de un sistema secuencial síncrono se dicen equivalentes si para cualquier secuencia de entradas producen la misma secuencia de salidas.

- esta relación de equivalencia permite clasificar los estados en clases, siendo necesario considerar un estado por clase.

- La relación de equivalencia entre estados se traduce en que dos estados son equivalentes si para cada entrada individual producen la misma salida y los estados siguientes son equivalentes.

Electrónica Digital - Circuitos lógicos secuenciales

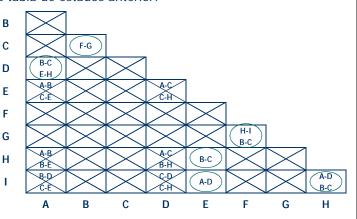

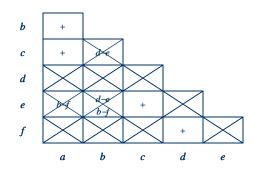

## Implementación y minimización

- > El procedimiento de síntesis de sistemas secuenciales síncronos puede resumirse en:

- ✓ obtención de la tabla de estados y eliminación de estados innecesarios u obviamente equivalentes

- ✓ construcción de la tabla de implicaciones

- √ búsqueda de las clases de equivalencia máximas

- ✓ asignación de estados

- ✓ síntesis de salidas y excitaciones de los biestables

- La tabla de implicaciones permite la búsqueda sistemática de estados equivalentes a partir de la tabla de estados.

- > Tras finalizar la tabla, sólo es necesario un estado por cada clase de equivalencia obtenida.

# Implementación y minimización

> **Ejemplo:** diseñar un circuito de una entrada y una salida que sintetice la tabla de estados siguiente:

|     | <i>x</i> =0 | <i>x</i> =1 |   |

|-----|-------------|-------------|---|

| Α   | B,0         | E,0         |   |

| B   | C,1         | F,0         |   |

| C   | B,1         | G,0         |   |

| D   | C,0         | H,0         |   |

| Е   | A,0         | C,0         |   |

| F   | H,1         | C,1         |   |

| G   | 1,1         | J,1         |   |

| Н   | A,0         | B,0         |   |

| - 1 | D,0         | C,0         |   |

| J   | C,1         | F,0         | b |

|    | <i>x</i> =0 | <i>x</i> =1 |

|----|-------------|-------------|

| Α  | В,0         | E,0         |

| В  | C,1         | F,0         |

| С  | B,1         | G,0         |

| D  | C,0         | H,0         |

| Ε  | A,0         | C,0         |

| F  | H,1         | C,1         |

| G  | 1,1         | B,1         |

| Н  | A,0         | B,0         |

| -1 | D,0         | C,0         |

|    |             |             |

Electrónica Digital - Circuitos lógicos secuenciales

# Implementación y minimización

> **Ejemplo:** diseñar un circuito de una entrada y una salida que sintetice la tabla de estados anterior:

|   | <i>x</i> =0 | <i>x</i> =1 |

|---|-------------|-------------|

| Α | В,0         | E,0         |

| В | C,1         | F,0         |

| С | B,1         | G,0         |

| D | C,0         | H,0         |

| Ε | A,0         | C,0         |

| F | H,1         | C,1         |

| G | 1,1         | B,1         |

| Н | A,0         | B,0         |

| 1 | D,0         | C,0         |

|   |             |             |

|   |             |             |

## Implementación y minimización

- > **Ejemplo:** diseñar un circuito de una entrada y una salida que sintetice la tabla de estados anterior:

- ✓ Clases de equivalencia

- $\circ$  (A,D)  $\rightarrow$  a

- $\circ$  (B,C) → b

- $\circ$  (F,G)  $\rightarrow$  c

- $o(E,H,I) \rightarrow d$

|   | <i>x</i> =0 | <i>x</i> =1 |

|---|-------------|-------------|

| а | b,0         | d,0         |

| b | b,1         | с,0         |

| С | d,1         | b,1         |

| d | a,0         | b,0         |

- ✓ Asignación de estados

- los estados con los mismos estados siguientes en todas las columnas han de recibir asignaciones adyacentes

- o los estados siguientes a un cierto estado situados en columnas adyacentes es recomendable que cuenten con asignaciones adyacentes

- ${\tt o}$  las asignaciones deben de simplificar en lo posible las funciones de salida

Electrónica Digital - Circuitos lógicos secuenciales

### **Sumario**

- > Introducción: elementos de memoria y registros

- Contadores

- ✓ Contadores síncronos y asíncronos

- ✓ Contadores con registros de desplazamiento

- Sistemas secuenciales síncronos

- ✓ Máquinas de estados finitos: máquinas Mealy y Moore

- ✓ Implementación y minimización

- > Sistemas secuenciales asíncronos

- ✓ Definición y síntesis

- ✓ Ciclos, carreras y riesgos

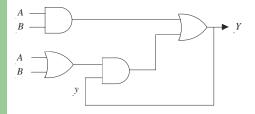

#### Sistemas secuenciales asíncronos

- Un sistema secuencial asíncrono es un sistema secuencial que evoluciona en respuesta a cualquier cambio en las entradas, sin necesidad de una señal de reloj.

- Estos sistemas son muy útiles cuando es necesaria una alta velocidad de respuesta, ya que no se ha de sincronizar el funcionamiento con la señal de reloj.

- > También son aplicables en situaciones en las que se requiere un comportamiento más complejo que el puramente combinacional pero no hay disponible una señal de reloj.

Electrónica Digital - Circuitos lógicos secuenciales

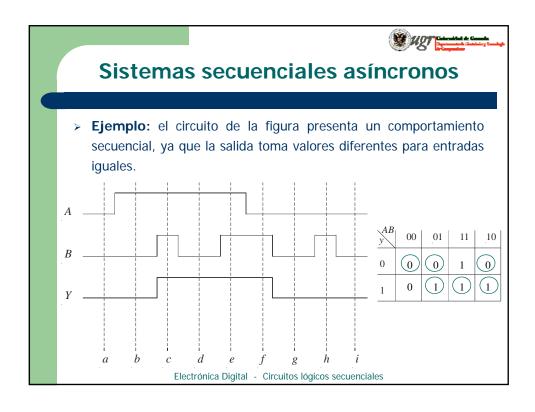

#### Sistemas secuenciales asíncronos

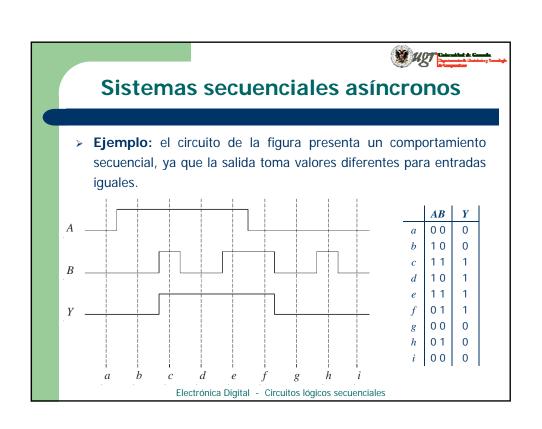

> **Ejemplo:** el circuito de la figura presenta un comportamiento secuencial, ya que la salida toma valores diferentes para entradas iguales.

| AB | 00 | 01 | 11 | 10 |

|----|----|----|----|----|

| 0  | 0  | 0  | 1  | 0  |

| 1  | 0  | 1  | 1  | 1  |

#### Sistemas secuenciales asíncronos

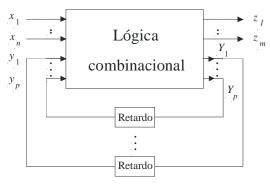

La estructura básica de los sistemas secuenciales asíncronos es un bloque combinacional con n entradas externas, p variables internas, m salidas externas y p variables de excitación.

Electrónica Digital - Circuitos lógicos secuenciales

# Síntesis y minimización

► Ejemplo: diseñar un circuito con una entrada x, una entrada de control C y una salida z, de modo que z sea 0 salvo cuando ocurra un flanco en x y C=1, manteniendo z a 1 hasta que C=0.

|              | Cx |    |                |            | z  |    |    |    |  |  |

|--------------|----|----|----------------|------------|----|----|----|----|--|--|

| \            | 00 | 01 | 11             | 10         | 00 | 01 | 11 | 10 |  |  |

|              | a  | с  | _              | b          | 0  | 0  | -  | 0  |  |  |

| $\bigcirc b$ | а  | _  | d              | <b>(b)</b> | 0  | -  | -  | 0  |  |  |

| $\bigcirc$   | а  | c  | e              | -          | 0  | 0  | 0  | -  |  |  |

| d            | _  | c  | $\overline{d}$ | f          | _  | -  | 1  | 1  |  |  |

| e            | _  | c  | e              | f          | _  | 0  | 0  | -  |  |  |

| f            | а  | _  | d              | (f)        | -  | _  | 1  | 1  |  |  |

Electrónica Digital - Circuitos lógicos secuenciales

# Síntesis y minimización

► Ejemplo: diseñar un circuito con una entrada x, una entrada de control C y una salida z, de modo que z sea 0 salvo cuando ocurra un flanco en x y C=1, manteniendo z a 1 hasta que C=0.

| -\                       | Cx  |            |     |               |    | 2  |    |    |

|--------------------------|-----|------------|-----|---------------|----|----|----|----|

| \                        | 00  | 01         | 11  | 10            | 00 | 01 | 11 | 10 |

|                          | (a) | c          | _   | b             | 0  | 0  | _  | 0  |

| (b)                      | а   | _          | d   | <b>(b</b> )   | 0  | _  | _  | 0  |

| $\bigcirc$               | a   | $\bigcirc$ | e   | _             | 0  | 0  | 0  | -  |

| (d)                      | _   | c          | (d) | f             | _  | _  | 1  | 1  |

| $\stackrel{e}{\bigcirc}$ | _   | c          | e   | f             | -  | 0  | 0  | -  |

| (f)                      | а   | _          | d   | $\widehat{f}$ | -  | _  | 1  | 1  |

Electrónica Digital - Circuitos lógicos secuenciales

# Síntesis y minimización

- ► Ejemplo: diseñar un circuito con una entrada x, una entrada de control C y una salida z, de modo que z sea 0 salvo cuando ocurra un flanco en x y C=1, manteniendo z a 1 hasta que C=0.

- ✓ clases de compatibilidad:

- o (a,b)

- o (a,c)

- o (c,e)

- o (df)

- $\circ$  cobertura mínima con (a,b), (c,e) y (d,f)

# Síntesis y minimización

► Ejemplo: diseñar un circuito con una entrada x, una entrada de control C y una salida z, de modo que z sea 0 salvo cuando ocurra un flanco en x y C=1, manteniendo z a 1 hasta que C=0.

|                 | Cx | $Y_1$ | -  |    |    | z  |    |    |  |  |

|-----------------|----|-------|----|----|----|----|----|----|--|--|

| $y_1y_0$        | 00 | 01    | 11 | 10 | 00 | 01 | 11 | 10 |  |  |

| $A \bigcirc 00$ | 00 | 01    | 11 | 00 | 0  | 0  | -  | 0  |  |  |

| B(01)           | 00 | 01    | 01 | 11 | 0  | 0  | 0  | -  |  |  |

| C(11)           | 00 | 01    | 11 | 11 | -  | -  | 1  | 1  |  |  |

| 10              |    |       |    |    | -  | 1  | 1  | -  |  |  |

Electrónica Digital - Circuitos lógicos secuenciales

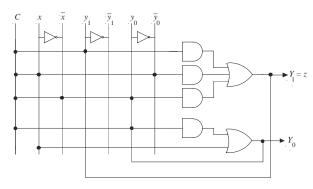

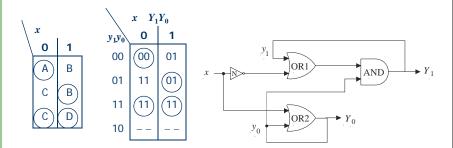

# Síntesis y minimización

► Ejemplo: diseñar un circuito con una entrada x, una entrada de control C y una salida z, de modo que z sea 0 salvo cuando ocurra un flanco en x y C=1, manteniendo z a 1 hasta que C=0.

## Ciclos y carreras

- > En un circuito secuencial asíncrono hay un ciclo si:

- ✓ en la transición entre dos estados estables se pasa por varios estados inestables, pero...

- ✓ en cada paso sólo cambia una variable secundaria (interna).

- > En un circuito secuencial asíncrono hay un carrera no crítica si:

- en la transición entre dos estados estables es necesario el cambio de más de una variable secundaria, pero...

- ✓ cualquiera que sea el orden del cambio se llega al estado deseado.

- > En un circuito secuencial asíncrono hay un carrera crítica si:

- ✓ en la transición entre dos estados estables es necesario el cambio de más de una variable secundaria, pero...

- ✓ dependiendo del camino seguido se llega a diferentes estados finales.

Electrónica Digital - Circuitos lógicos secuenciales

## Ciclos y carreras

- > Ciclos y carreras no críticas no suponen un riesgo en sí mismos.

- Las carreras críticas han de evitarse en los sistemas asíncronos, ya que son una fuente de errores:

- ✓ en el ejemplo anterior, si  $y_1y_0Cx$ =0010 y x cambia a 1 se pasa del estado 00 al 11, pasando por el inestable 11;

- ✓ sin embargo, un cambio en x afecta a  $Y_0$  antes que a  $Y_1$ , con lo que el circuito puede acabar en el estado estable 01.

- Para eliminar las carreras críticas es necesario que los estados entre los que existen transiciones susceptibles de sufrir una carrera crítica reciban asignaciones adyacentes.

- en ocasiones es necesario incrementar el número de variables de estado a fin de conseguir asignaciones adecuadas.

## Ciclos y carreras

► Ejemplo: diseñar un circuito con una entrada x, una entrada de control C y una salida z, de modo que z sea 0 salvo cuando ocurra un flanco en x y C=1, manteniendo z a 1 hasta que C=0.

|          | Cx | $Y_1Y_0$ |      | z  |    |    |    |    |  |

|----------|----|----------|------|----|----|----|----|----|--|

| $y_1y_0$ | 00 | 01       | 11   | 10 | 00 | 01 | 11 | 10 |  |

| C(00)    | 01 | 10       | 00   | 00 | 0  | 0  | 1  | 1  |  |

| A(01)    | 01 | 10       | 00   | 01 | 0  | 0  | -  | 0  |  |

| 11       | 01 | 10       |      |    | 0  | 0  | -  | -  |  |

| B(10)    | 01 | (10)     | (10) | 00 | 0  | 0  | 0  | -  |  |

Electrónica Digital - Circuitos lógicos secuenciales

# Riesgos

- > Los riesgos propios de los circuitos combinacionales también aparecen en sistemas secuenciales asíncronos:

- ✓ los riesgos estáticos y dinámicos pueden traducirse en que los sistemas lleguen a estados incorrectos.

- ✓ pueden evitarse con idénticas precauciones que en circuitos combinacionales.

- Un circuito secuencial asíncrono además puede sufrir riesgos esenciales, cuando tres cambios consecutivos en una entrada llevan al circuito a un estado diferente al que lo lleva el primero de esos cambios.

# Riesgos

> **Ejemplo:** el sistema de la figura sufre un riesgo esencial:

➤ La única solución a los riesgos esenciales es introducir retardos en la realimentación para que los cambios en las entradas se propaguen antes de que cambie la realimentación.