# Sumario Memorias ROM Memoria ROM como módulo lógico universal Memorias RAM SRAM y DRAM Asociación de memorias Memorias FIFO y LIFO Estructuras lógicas programables PAL y PLA FPGA Electrónica Digital - Sistemas lógicos regulares

#### Introducción

- La creación de estructuras físicamente regulares (repetición espacial de los mismos elementos y conexiones) es una alternativa muy atractiva para el diseñador siempre que se disponga del área suficiente.

- Las tecnologías actuales de fabricación de circuitos integrados permiten la creación de estructuras enormemente complejas con gran cantidad de transistores en cada chip.

- Por tanto, una opción para la implementación de sistemas digitales, o al menos parte de los mismos, es el uso de estructuras complejas de estructura regular.

Electrónica Digital - Sistemas lógicos regulares

# **Sumario**

- Memorias ROM

- ✓ Memoria ROM como módulo lógico universal

- Memorias RAM

- ✓ SRAM y DRAM

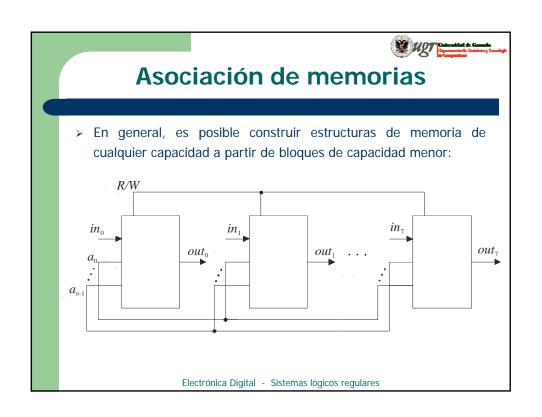

- ✓ Asociación de memorias

- ✓ Memorias FIFO y LIFO

- > Estructuras lógicas programables

- ✓ PAL y PLA

- ✓ FPGA

#### **Memorias ROM**

- > Una memoria de  $2^n$  palabras de m bits es una estructura lógica que consta de:

- √ n entradas de direcciones

- √ m salidas de datos

- $\checkmark$  2<sup>n</sup>×m celdas de memoria, en cada de una de las cuales se almacena un bit de información

- ✓ alternativamente puede contar con entradas de datos y de control.

- Cuando la información contenida en la memoria no puede alterarse, se dice que es una memoria de sólo lectura o ROM (Read-Only Memory).

Electrónica Digital - Sistemas lógicos regulares

#### **Memorias ROM**

- $\triangleright$  Una memoria de  $2^n$  palabras de m bits es una estructura lógica que consta de:

- $\checkmark$  *n* entradas de direcciones

- √ m salidas de datos

- $\checkmark$  2<sup>n</sup>×m celdas de memoria, en cada de una de las cuales se almacena un bit de información

- $\checkmark\,$  alternativamente puede contar con entradas de datos y de control.

- Si es posible modificar la información contenida en la memoria, para ello será necesario incluir entradas de control y datos, estando ante ROMs programables (PROM) o memorias de acceso aleatorio o RAM (Random Access Memory)

#### **Memorias ROM**

- ➢ En cualquier tipo de memoria a cada palabra le corresponde una dirección única, formada por una de las 2<sup>n</sup> combinaciones posibles de los n bits de dirección.

- > De este modo, cualquier circuito combinacional de *n* entradas y *m* salidas funciona como una memoria permanente o ROM:

- ✓ multiplexores

- ✓ decodificadores

- Sin embargo, la denominación de memoria permanente se reserva para las memorias ROM, en sus diferentes configuraciones.

Electrónica Digital - Sistemas lógicos regulares

# **Memorias ROM**

> Una memoria ROM puede interpretarse como un conversor de código, ya que asigna a un carácter de *n* bits otro de *m* bits.

#### **Memorias ROM**

- ➤ Una memoria ROM puede interpretarse como un conversor de código, ya que asigna a un carácter de *n* bits otro de *m* bits.

- > De este modo, variando el conexionado de la matriz OR es posible programar el contenido de la memoria ROM:

- ✓ PROM: *Programmable* ROM

- ✓ EPROM: Erasable and Programmable ROM

- ✓ EEPROM: *Electrically Erasable and Programmable* ROM

- > En consecuencia, la memoria ROM es uno de los elementos más utilizados en sistemas digitales: tablas, módulo lógico, etc.

Electrónica Digital - Sistemas lógicos regulares

# **Sumario**

- > Memorias ROM

- ✓ Memoria ROM como módulo lógico universal

- > Memorias RAM

- ✓ SRAM y DRAM

- ✓ Asociación de memorias

- ✓ Memorias FIFO y LIFO

- > Estructuras lógicas programables

- ✓ PAL y PLA

- ✓ FPGA

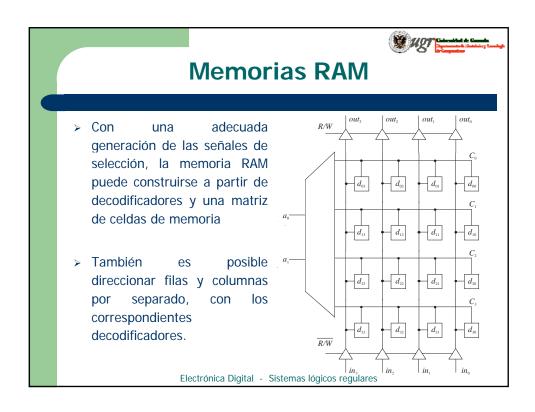

#### **Memorias RAM**

- Una memoria RAM (*Random Access Memory*) no sólo permite la lectura de una determinada palabra, sino también su escritura durante el funcionamiento normal de la memoria:

- mantienen la información almacenada en ellas mientras el circuito esté alimentado

- ✓ la denominación "acceso aleatorio" hace referencia a que no está prefijado el orden de acceso a las palabras de la memoria

- > El propio concepto de memoria RAM implica la necesidad de una celda básica de memoria:

- ✓ SRAM (Static RAM): la celda mantiene la información contenida

- ✓ DRAM (*Dynamic* RAM): la celda requiere refrescar la información

Electrónica Digital - Sistemas lógicos regulares

#### **Memorias RAM**

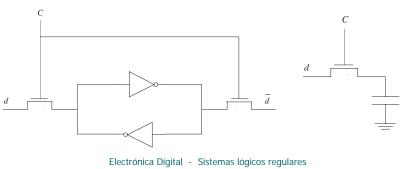

- > La celda básica ha de permitir tanto la lectura como la escritura, con conexionado y recursos mínimos:

- ✓ una señal C habilita el acceso a la celda

- $\checkmark$  en una operación de lectura, se fuerza el valor del dato d, mientras que en una de lectura d fija el valor de la línea

# Memorias LIFO y FIFO

- Ambos tipos de memoria son estructuras de almacenamiento de datos especiales, muy útiles en sistemas digitales, especialmente para la gestión de:

- √ colas (First Input First Output)

- √ pilas (Last Input First Output)

- Son parte básica de muchos sistemas digitales complejos en los que se requiere acceso secuencial a los datos.

- Se pueden construir a base de registros de desplazamiento o sobre RAM, usando contadores, como ocurre en muchos microprocesadores.

Electrónica Digital - Sistemas lógicos regulares

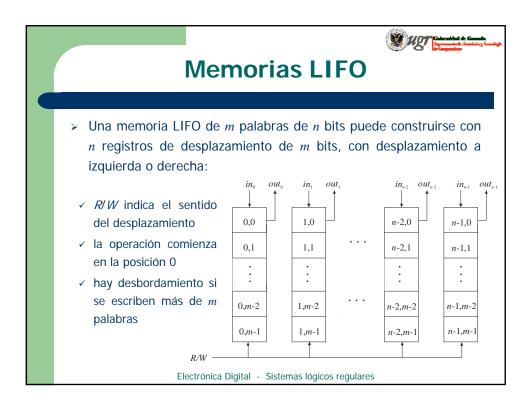

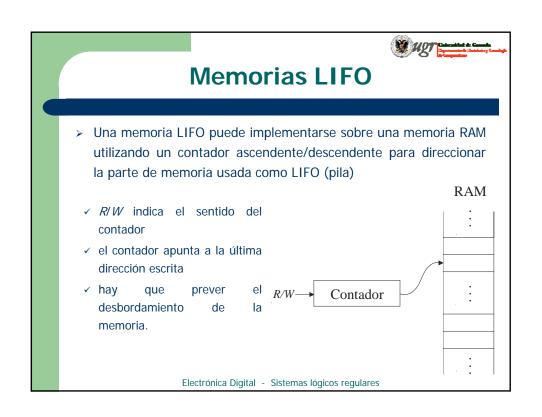

#### **Memorias LIFO**

- Una memoria LIFO (Last Input First Output) es una memoria de acceso secuencial con un único punto de acceso, tanto para lectura como para escritura.

- > Su funcionamiento es muy sencillo:

- ✓ siempre se lee la última posición escrita aún no leída

- ✓ siempre se escribe en la primera posición aún no escrita (libre)

- > Una de las principales aplicaciones de las memorias LIFO es la implementación de pilas: el método de lectura/escritura simula el apilamiento de los datos almacenados.

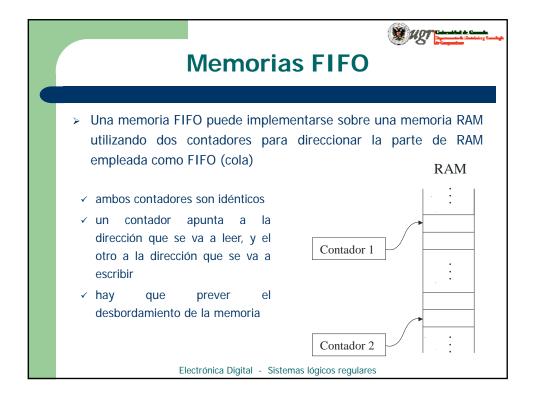

#### **Memorias FIFO**

- > Una memoria FIFO (First Input First Output) es una memoria de acceso secuencial con dos puntos de acceso, uno para lectura y otro para escritura.

- > Su funcionamiento es muy sencillo:

- ✓ siempre se lee la primera palabra escrita aún no leída

- ✓ siempre se escribe en la última posición aún no escrita (libre)

- Una de las principales aplicaciones de las memorias LIFO es la implementación de colas: el método de lectura/escritura simula el funcionamiento de una cola.

Electrónica Digital - Sistemas lógicos regulares

#### **Memorias FIFO**

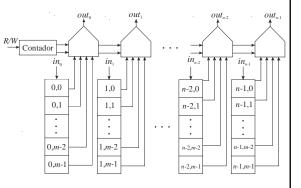

- Una memoria FIFO de m palabras de n bits puede construirse con n registros de desplazamiento de m bits, un contador ascendente/descendente y multiplexores:

- √ R/W controla e

contador

- ✓ siempre se escribe en la posición 0

- el contador también permite controlar el desbordamiento

# Estructuras lógicas programables

- > La tecnología actual permite crear circuitos integrados de gran complejidad y precio reducido.

- Sin embargo, el coste de desarrollo de un ASIC (Application Specific Integrated Circuit) sólo es justificable en el caso de grandes volúmenes de producción.

- > Además del coste, el tiempo de producción de prototipos puede influir negativamente en el ciclo de diseño.

- > Por tanto, el disponer de estructuras programables es una alternativa muy interesante tanto para el prototipado como para pequeños volúmenes de producción.

Electrónica Digital - Sistemas lógicos regulares

# Estructuras lógicas programables

- > Existen diferentes tipos de dispositivos programables:

- ✓ ROM

- ✓ PAL y PLA

- ✓ FPGA (y sus diferentes variantes)

- > Estos dispositivos permiten, a partir de un determinado chip virgen, la implementación de diferentes circuitos lógicos.

- También existen diferentes tecnologías para la programación de dichos dispositivos.

- > Las FPGAs (y sus variantes) han revolucionado el mundo del diseño digital, por su versatilidad y facilidad de programación.

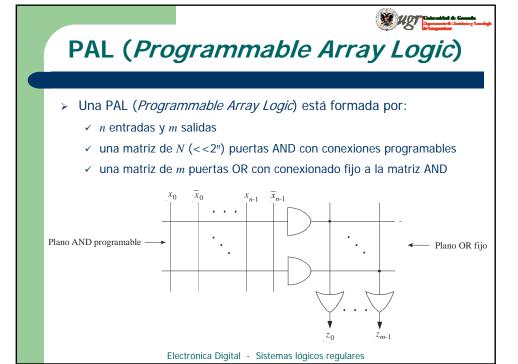

# PAL y PLA

- La estructura mostrada de la ROM corresponde a un plano AND fijo (selección de palabra) y un plano OR programable (contenido).

- De manera análoga, se pueden definir estructuras programables más flexibles:

- ✓ PAL (*Programmable Array Logic*): plano AND programable junto a un plano OR fijo

- ✓ PLA (*Programmable Logic Array*): planos AND y OR programables

- Estas estructuras permiten una mayor flexibilidad que la ROM, aunque las tecnologías y técnicas de programación son muy similares, permitiendo el uso de un mismo dispositivo para la síntesis de diferentes sistemas lógicos.

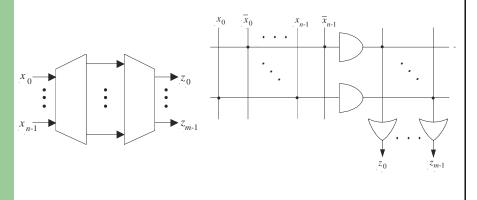

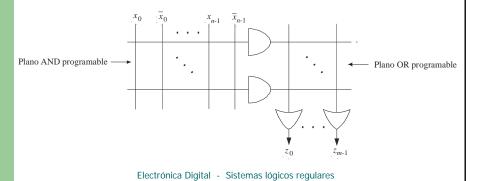

# PLA (Programmable Logic Array)

- > Una PLA (*Programmable Logic Array*) está formada por:

- √ n entradas y m salidas

- ✓ una matriz de N (<<2 $^n$ ) puertas AND con conexiones programables

- $\checkmark$  una matriz de m puertas OR con conexionado programable

# FPGA (Field-Programmable Gate Array)

- Las FPGAs (Field-Programmable Gate Array), en sus diferentes variantes, son una de las últimas innovaciones en el desarrollo de sistemas digitales:

- ✓ facilidad de programación y configuración (ROM, JTAG, etc.)

- ✓ gran capacidad (existen dispositivos que equivalen a varios millones de puertas lógicos)

- permiten el prototipado de sistemas complejos sin necesidad de la fabricación de prototipos ASIC, reduciendo los costes y la duración del desarrollo

- √ para aplicaciones específicas, permiten la implementación de sistemas complejos evitando los costes de desarrollo de un ASIC

- ✓ posibilidad de reconfiguración dinámica

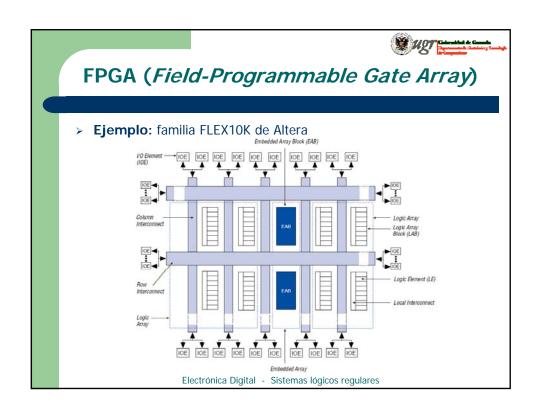

#### FPGA (Field-Programmable Gate Array)

- Usualmente, una FPGA difiere de la filosofía de los dispositivos programables anteriores:

- ✓ en lugar de dos niveles AND-OR programables, la FPGA incluye una matriz de elementos idénticos y programables (elemento lógico), unidas por una red de interconexiones programables.

- √ para la implementación flexible de sistemas secuenciales, cada elemento lógico incluye un biestable en la salida.

- > Este tipo de estructura permite la implementación de sistemas más complejos que las estructuras anteriores.

- Normalmente, estos dispositivos están basados en tecnología SRAM, lo que permite una fácil reprogramación.

Electrónica Digital - Sistemas lógicos regulares

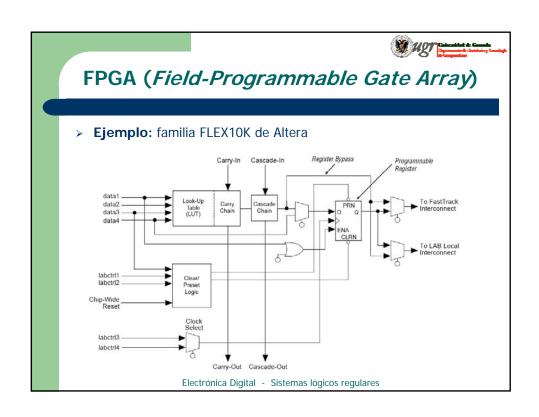

#### FPGA (Field-Programmable Gate Array)

- > En la mayoría de dispositivos, el elemento lógico básico está formado por:

- ✓ una tabla de consulta (LUT: Look-Up Table) de 4 entradas y una salida (2<sup>4</sup>×1 bits) en la que se puede almacenar cualquier función de conmutación de 4 variables

- ✓ un biestable que puede o no tomar su entrada de la tabla anterior

- ✓ lógica adicional de control y para la implementación de funciones aritméticas

- > Las últimas generaciones también incorporan:

- ✓ bloques específicos para la implementación de memoria

- ✓ circuitos aritméticos de alta velocidad (orientados a DSP)