### Wag ....

## **Sumario**

- > BJT y MOSFET en circuitos digitales

- ✓ Caracterización de circuitos digitales electrónicos

- ✓ Inversor básico bipolar

- ✓ Inversor básico MOS

- > Familias lógicas: CMOS

- ✓ Análisis del inversor CMOS

- ✓ Puertas CMOS comerciales

- > Circuitos de interfase

- √ Fan-in y fan-out

- ✓ Acceso a buses

#### Introducción

- Los sistemas digitales mostrados hasta ahora son independientes de la implementación física de las señales digitales y las puertas lógicas.

- > La implementación más frecuente es la electrónica:

- ✓ señales digitales: niveles discretos de tensión

- ✓ puertas lógicas: construidas a partir de transistores

- Si bien la estructura y metodología de diseño no se ven afectados por la implementación física, si es necesario considerar las diferencias entre el funcionamiento real y el comportamiento "ideal" de niveles lógicos y puertas.

Electrónica Digital - Familias lógicas integradas

## **Sumario**

- > BJT y MOSFET en circuitos digitales

- ✓ Caracterización de circuitos digitales electrónicos

- ✓ Inversor básico bipolar

- ✓ Inversor básico MOS

- > Familias lógicas: CMOS

- ✓ Análisis del inversor CMOS

- ✓ Puertas CMOS comerciales

- Circuitos de interfase

- √ Fan-in y fan-out

- Acceso a buses

#### Caracterización de circuitos digitales

- Los circuitos digitales basados en tecnología electrónica hacen uso de magnitudes eléctricas para definir los niveles lógicos:

- ✓ en un comportamiento ideal, dos valores discretos de tensión corresponden al 1 y 0 lógicos

- en un circuito real no es posible conseguir las tensiones exactas que corresponde a 1 ó 0, con lo que se hace necesario definir ciertos márgenes de funcionamiento

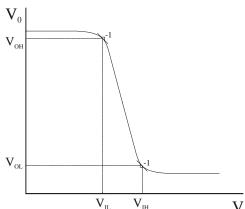

- La relación entre niveles de tensión y niveles lógicos se establece a partir de la característica de transferencia del inversor (operador NOT)

- > La característica de transferencia del inversor permite definir diferentes niveles lógicos característicos.

Electrónica Digital - Familias lógicas integradas

### Caracterización de circuitos digitales

- Los puntos de pendiente –1 permiten definir los niveles lógicos de entrada y salida:

- √ V<sub>IH</sub>: valor mínimo interpretado como 1

- ✓ V<sub>IL</sub>: valor máximo interpretado como 0

- √ V<sub>OH</sub>: valor mínimo proporcionado como 1

- ✓ V<sub>oL</sub>: valor máximo proporcionado como 0

### Caracterización de circuitos digitales

> El funcionamiento correcto de una familia lógica exige que los niveles lógicos guarden cierta relación:

$$\begin{array}{c|cccc} V_{IH} < V_{OH} & V_{IL} > V_{OL} \\ \hline \hline V_{OH} & V_{IH} \\ \hline NMH & V_{IH} \\ \hline \hline V_{OL} & \hline V_{IL} \\ \hline \end{array}$$

> Los márgenes de ruido son:

$$NMH = V_{OH} - V_{IH}$$

$$NML = V_{IL} - V_{OL}$$

Electrónica Digital - Familias lógicas integradas

## **y**ugr

### Caracterización de circuitos digitales

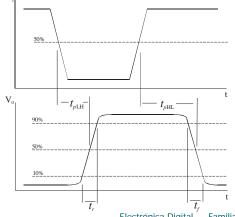

> El comportamiento dinámico queda definido por los diferentes retardos asociados a las transiciones entre niveles lógicos

- $\checkmark$   $t_{pHL}$ : tiempo de propagación (1 a 0, 50% de la transición de entrada hasta 50% de la transición de salida)

- $t_{pLH}$ : tiempo de propagación (0 a 1, 50% de la transición de entrada hasta 50% de la transición de salida)

- √ t<sub>r</sub>: tiempo de subida (10-90%)

- $\checkmark$   $t_f$ : tiempo de bajada (90-10%)

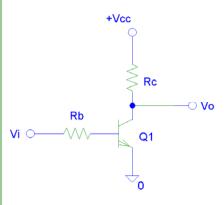

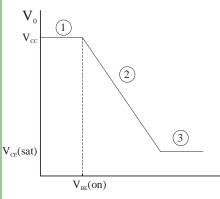

## Inversor básico bipolar

La habilidad de los transistores para conducir o no según una variable de control permite definir puertas lógicas electrónicas

1.  $V_i < V_{BE}(on)$ : Q1 en **corte**, de modo que:

$$V_0 = V_{CC} - I_C R_C = V_{CC}$$

2.  $V_i > V_{BE}(on)$ : Q1 en conducción, con  $V_C > V_B$  y Q1 en **activa**:

$$V_0 = V_{CC} - I_C R_C = V_{CC} - \beta R_C / R_B [V_i - V_{BE}(on)]$$

3.  $V_i \uparrow \uparrow$ :  $V_B > V_C$  y Q1 en **saturación**:  $V_0 = V_{CE}(sat) \approx 0.2V$

Electrónica Digital - Familias lógicas integradas

# Inversor básico bipolar

La habilidad de los transistores para conducir o no según una variable de control permite definir puertas lógicas electrónicas

1.  $V_i < V_{BE}(on)$ : Q1 en **corte**, de modo que:

$$V_0 = V_{CC} - I_C R_C = V_{CC}$$

2.  $V_i > V_{BE}(on)$ : Q1 en conducción, con  $V_c > V_B$  y Q1 en **activa**:

$$V_0 = V_{CC} - I_C R_C = V_{CC} - \beta R_C / R_B [V_i - V_{BE}(on)]$$

3. V<sub>i</sub>↑↑: V<sub>B</sub>>V<sub>C</sub> y Q1 en **saturación**: V<sub>0</sub>=V<sub>CF</sub>(sat)≈0.2V

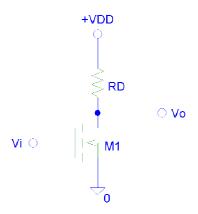

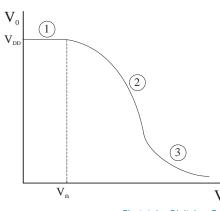

#### Inversor básico MOS

La habilidad de los transistores para conducir o no según una variable de control permite definir puertas lógicas electrónicas

1.  $V_i < V_{th}$ : M1 en **corte**, de modo que:

$$V_0 = V_{DD} - I_D R_D = V_{DD}$$

- 2.  $V_i > V_{th}$ : M1 en conducción, con  $V_{DS} > V_{GS} V_{th}$  y M1 en **saturación**:  $V_0 = V_{DD} I_D R_D = V_{DD} R_D \beta/2 (V_i V_{th})^2$

- 3.  $V_i \uparrow \uparrow$ :  $V_{DS} < V_{GS} V_{th}$  y M1 en **zona** lineal:

$$V_0 = V_{DD} - R_D \beta / 2[2(V_i - V_{th}) - V_0]V_0$$

Electrónica Digital - Familias lógicas integradas

### **Inversor básico MOS**

La habilidad de los transistores para conducir o no según una variable de control permite definir puertas lógicas electrónicas

1.  $V_i < V_{th}$ : M1 en **corte**, de modo que:

$$V_0 = V_{DD} - I_D R_D = V_{DD}$$

- 2.  $V_i > V_{th}$ : M1 en conducción, con  $V_{DS} > V_{GS} V_{th} \ y \ M1 \ en \ \textbf{saturación}$ :  $V_0 = V_{DD} I_D R_D = V_{DD} R_D \beta/2 (V_i V_{th})^2$

- 3.  $V_i \uparrow \uparrow \uparrow$ :  $V_{DS} < V_{GS} V_{th}$  y M1 en **zona** lineal:

$$V_0 = V_{DD} - R_D \beta / 2[2(V_i - V_{th}) - V_0]V_0$$

#### **Sumario**

- > BJT y MOSFET en circuitos digitales

- ✓ Caracterización de circuitos digitales electrónicos

- ✓ Inversor básico bipolar

- ✓ Inversor básico MOS

- > Familias lógicas: CMOS

- ✓ Análisis del inversor CMOS

- ✓ Puertas CMOS comerciales

- > Circuitos de interfase

- √ Fan-in y fan-out

- ✓ Acceso a buses

Electrónica Digital - Familias lógicas integradas

## Familias lógicas: CMOS

- ➤ El término "familia lógica" hace referencia a conjuntos de puertas y elementos lógicos que usan una misma disposición interna de los transistores y el mismo tipo de funcionamiento.

- > Entre las familias lógicas más comunes destacan:

- NMOS: puertas lógicas formadas por transistores nMOS (velocidad y consumo moderados, gran densidad)

- ✓ CMOS: puertas lógicas formadas por transistores nMOS y pMOS (velocidad y densidad elevados, consumo reducido)

- ✓ TTL: puertas lógicas formadas por transistores BJT (velocidad, consumo y densidad moderados)

- ✓ ECL: puertas lógicas formadas por transistores BJT en par acoplado por emisor (gran velocidad y consumo, densidad reducida)

## Familias lógicas: CMOS

- ➤ La lógica CMOS (*Complementary MOS*) recibe este nombre ya que las puertas están formadas por transistores nMOS y pMOS.

- > La lógica CMOS es la más utilizada en la actualidad por sus ventajas evidentes frente al resto de familias lógicas:

- ✓ consumo: idealmente, una puerta CMOS sólo consume energía durante la conmutación entre estados lógicos (por tanto, el consumo es proporcional a la frecuencia de conmutación)

- ✓ capacidad de integración: dado su consumo reducido, la densidad de empaquetamiento CMOS es muy elevada

- velocidad: la lógica CMOS permite una velocidad de funcionamiento muy elevada con retardos simétricos

Electrónica Digital - Familias lógicas integradas

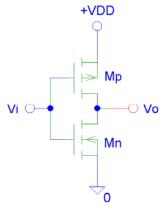

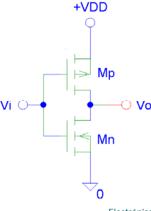

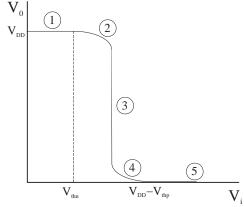

### Análisis del inversor CMOS

$\gt$  El inversor CMOS está formado por un transistor nMOS y otro pMOS que conectan la salida alternativamente a  $V_{DD}$  ó 0:

1.  $V_i < V_{thn}$ : Mn en **corte** y Mp en **zona lineal**:

$$\begin{split} I_{Dn} = & 0 \! = \! I_{Dp} \Longrightarrow V_0 \! = \! V_{DD} \\ & (\beta_p \! / \! 2 [2(V_i \! - \! V_{DD} \! - \! V_{thp}) \! - \! (V_0 \! - \! V_{DD})] (V_0 \! - \! V_{DD}) \! = \! 0 ) \end{split}$$

$$\begin{split} I_{Dn} &= I_{Dp} \Rightarrow \beta_n / 2 (V_i \!\!-\!\! V_{thn})^2 = \\ &= \beta_p / 2 [2 (V_i \!\!-\!\! V_{DD} \!\!-\!\! V_{thp}) \!\!-\!\! (V_0 \!\!-\!\! V_{DD})] (V_0 \!\!-\!\! V_{DD}) \end{split}$$

#### Análisis del inversor CMOS

$\gt$  El inversor CMOS está formado por un transistor nMOS y otro pMOS que conectan la salida alternativamente a  $V_{DD}$  ó 0:

- 3.  $V_i \uparrow \uparrow$ : Mn y Mp en **saturación**:  $\beta_n/2(V_i V_{thn})^2 = \beta_p/2(V_i V_{DD} V_{thp})^2 \Rightarrow$  $\Rightarrow V_0 = V_{DD}/2 \text{ (inversor simétrico)}$

- 4.  $V_i \uparrow \uparrow$ : Mn en **zona lineal** y Mp en **saturación**:

$$\beta_p/2(V_i-V_{DD}-V_{thp})^2=\beta_n/2[2(V_i-V_{thn})-V_0]V_0$$

5.  $V_i > V_{DD} - V_{thp}$ : Mn en **zona lineal** y Mp en **corte**:

$$I_{Dn} = 0 = I_{Dp} \Rightarrow \beta_n / 2[2(V_i - V_{thn}) - V_0]V_0 = 0 \Rightarrow V_0 = 0$$

Electrónica Digital - Familias lógicas integradas

## **Análisis del inversor CMOS**

$\succ$  El inversor CMOS está formado por un transistor nMOS y otro pMOS que conectan la salida alternativamente a  $V_{DD}$  ó 0:

#### Análisis del inversor CMOS

Del análisis de las zonas 2 y 4 de la característica de transferencia del inversor CMOS se pueden deducir los valores de V<sub>II</sub> y V<sub>IH</sub>:

$$V_{IL} = 1/8(3V_{DD} + 2V_{th})$$

$V_{IH} = 1/8(5V_{DD} - 2V_{th})$

> Si se considera  $V_{OL}$ ≈0 y  $V_{OH}$  ≈ $V_{DD}$ , los márgenes de ruido CMOS son:

$$NMH = NML = 1/8(3V_{DD} + 2V_{th})$$

Si la entrada permanece constante, el inversor CMOS no consume energía, ya que no circula corriente e, idealmente, el circuito sólo consume en las transiciones entre estados.

Electrónica Digital - Familias lógicas integradas

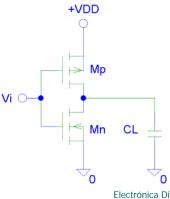

## Análisis del inversor CMOS

➤ En lo que se refiere al comportamiento dinámico, la carga en circuitos digitales puede modelarse a través de una capacidad (tanto para familias MOS como familias bipolares):

- √ 0→1: el condensador ha de cargarse hasta V<sub>OH</sub>, lo que hace con la corriente suministrada por el transistor pMOS

- $1\rightarrow 0$ : el condensador ha de descargarse hasta  $V_{OL}$ , lo que hace a través del transistor nMOS

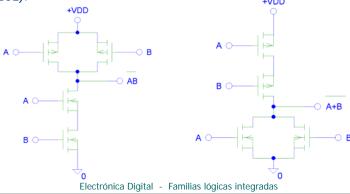

## **Puertas lógicas CMOS**

La lógica CMOS (al igual que la nMOS) permite definir de manera natural puertas NAND y NOR, frente a las lógicas bipolares, que tienen como bloque básico la puerta NAND (TTL) u OR/NOR (ECL).

## **Puertas CMOS comerciales**

- Existen diferentes series comerciales de circuitos digitales SSI (Small Scale Integration) y MSI (Medium Scale Integration) de las que la más popular es la serie 74.

- > Existen variantes de la familia 74 en diferentes tecnologías: TTL, BiCMOS y CMOS, con diferentes series en cada tecnología.

- > La familia 74 incluye:

- √ buffers, drivers y puertas lógicas discretas

- ✓ decodificadores, codificadores, multiplexores y demultiplexores

- ✓ elementos de memoria

- ✓ contadores y otra lógica especializada (sumadores, etc.)

#### **Puertas CMOS comerciales**

- Las diferentes variantes de la familia 74 permiten un amplio rango de selección de un mismo elemento: coste, velocidad, encapsulado, etc., normalmente compatibles entre fabricantes diferentes.

- ➤ **Ejemplo:** el chip 74AC00 incluye cuatro puertas NAND, puede alimentarse entre 2V y 6V y está disponible en diferentes encapsulados (DIP, SOIC, SOP, PDIP, etc.)

- > Más información en:

- ✓ Texas Instruments (http://www.ti.com/)

- ✓ Fairchild Semiconductor (http://www.fairchildsemi.com/)

Electrónica Digital - Familias lógicas integradas

#### **Sumario**

- > BJT y MOSFET en circuitos digitales

- ✓ Caracterización de circuitos digitales electrónicos

- ✓ Inversor básico bipolar

- ✓ Inversor básico MOS

- > Familias lógicas: CMOS

- ✓ Análisis del inversor CMOS

- ✓ Puertas CMOS comerciales

- > Circuitos de interfase

- √ Fan-in y fan-out

- ✓ Acceso a buses

#### Circuitos de interfase

- La interconexión entre sistemas digitales supone, en muchas ocasiones, la interconexión de circuitos de diferentes familias lógicas, lo que puede ocasionar problemas por:

- √ incompatibilidad entre los márgenes y niveles lógicos

- ✓ incompatibilidad entre las corrientes suministradas y/o absorbidas por las diferentes puertas

- Para evitar estos problemas es necesario elegir cuidadosamente los puntos de interconexión, insertando si es necesario buffers o drivers que adapten los diferentes niveles de tensión o corriente.

- > También es necesario observar ciertas precauciones en la interconexión de elementos de una misma familia lógica.

Electrónica Digital - Familias lógicas integradas

## Fan-iny fan-out

- Los términos fan-in y fan-out de una puerta lógica corresponden a las definiciones siguientes:

- √ fan-out: número de entradas de otras puertas a las que se conecta la salida de la puerta lógica en cuestión

- ✓ fan-in: número de entradas de la puerta en cuestión

- Aunque, en teoría, fan-in y fan-out podrían tomar cualquier valor, la implementación electrónica de los sistemas digitales lleva a definir fan-in y fan-out máximos de una familia lógica:

- fan-out máximo: número máximo de entradas de otras puertas a las que se puede conectar la salida de una puerta lógica manteniendo una interpretación correcta de los niveles lógicos

- ✓ fan-in máximo: número máximo de entradas de una puerta lógica que mantienen un funcionamiento correcto de dicha puerta

#### Acceso a buses

- En el caso de incluir buses en un sistema digital o simplemente cuando varias puertas comparten la misma carga, es necesario evitar la conexión directa ya que se puede generar un cortocircuito:

- ✓ si dos puertas intentan fijar la carga a valores lógicos diferentes, los transistores que fijan el 1 y el 0 en cada puerta quedan conectados

- en esta situación, aunque las entradas permanezcan fijas circula corriente por los transistores en conducción, lo que puede dañar el circuito

Electrónica Digital - Familias lógicas integradas

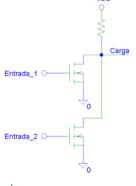

# Acceso a buses

- En el caso de incluir buses en un sistema digital o simplemente cuando varias puertas comparten la misma carga, es necesario evitar la conexión directa ya que se puede generar un cortocircuito:

- ✓ esto puede solventarse utilizando estructuras especiales, como una resistencia de pull-up

- ✓ en la figura, la carga siempre permanece con el valor lógico 1 salvo que una o más entradas traten de fijarla a 0, aunque pueden hacerlo de manera simultánea

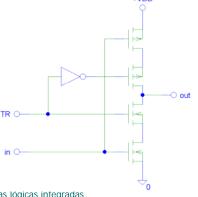

### Acceso a buses

- El acceso a buses o cargas compartidas también puede gestionarse con buffers o inversores tri-estado, que permiten conectar en cada momento una única fuente a la carga:

- ✓ si TR=1, el circuito de la figura funciona como un inversor CMOS

- ✓ si TR=0, los transistores nMOS y pMOS centrales no conducen, y la salida queda flotante, en lo que se conoce como alta impedancia (Z)